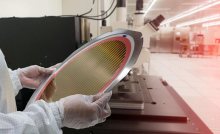

Sondrel以设计超大数字芯片闻名,秘诀在于利用片上网络保障数据在芯片的模块间正确流动。若是没有片上网络,芯片需要十倍以上的内存才能无延迟地进行相似的运算,这不经济。

理想设计中,所有需要高速、高数据流的模块应聚集在一起,即芯片中间的内存应靠近需要访问内存的IP(知识产权)核。事实上,除了高速缓存之外,内存位于芯片外,在由最先进内存技术打造的内存专用芯片上,因此内存的访问点位于芯片的外围。因此,需要一个复杂的网络来传送模块与模块之间,芯片与内存专用芯片之间的数据。大型芯片设计中可能包含多达十七层的水平互联加上大量层与层之间的垂直互联。

复杂数字芯片设计的十七个水平层及每层的互联布局

Sondrel片上网络专家Anne-Françoise Brenton 解释说:“这就像设计一个庞大的多层办工大楼,你的设计必须满足人员在不同区域和楼层间的最佳流动。当许多人需要在两个地点之间快速移动时,你需要一个宽阔的快速走廊,走廊的长度会影响人们到达的时间。同样,不常使用的非紧急路线可能又长又窄,因此速度很慢。垂直互联中也是类似的情况,有仅连接两个特定楼层以提供高速传输的专用大容量电梯,也有在所有楼层均停靠的慢速电梯。最重要的是仲裁,通过缓冲动态控制通过片上网络的数据流,随着需求不断平滑和优化,例如当两个IP块共享和访问同一内存时。”

在整个芯片的设计过程中,片上网络的设计是前端、后端和片上网络设计团队之间的迭代协作,因为每一部分的变化都会对他人的工作产生连锁影响。随着芯片布局前端设计的具体化,通过跟踪数据及其在缓存、片外内存或IP核中的位置,片上网络负载的仲裁需求也变得更加明确。

片上网络设计的难点在于第三方IP核可能是一个黑盒子。供应商处于保护IP核具体运作方法的目的,很少提供有关IP核所需数据流的信息。随着整个设计的成熟,上述困难迎刃而解。通过时序分析可以确保片上网络按照预先分配的优先级仲裁传递数据的路径,按照要求传递数据,克服了上述瓶颈。

Anne-Françoise Brenton总结道:“片上网络的设计就好似不断需要改变动作的杂耍表演。改变一个参数,其他东西也随之改变。像同时下多盘国际象棋一样,是个收获满满的智力挑战。”

关于Sondrel

Sondrel成立于2002年,是集成电路各阶段设计方面值得信赖的合作伙伴。 其在定义和设计专用集成电路方面的咨询能力屡获殊荣,为其将设计转化为经过测试的批量封装硅芯片的一站式服务提供了有力补充。整个供应链流程的单点联系,确保风险低,上市时间快。Sondrel总部位于英国,其通过在中国、印度、法国、摩洛哥和北美的办事处,为全球客户提供支持。更多信息,请访问www.sondrel.com/careers