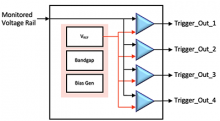

半导体行业目前的晶圆厂产能挑战导致ASIC和无晶圆厂公司评估多家代工厂,以满足未来几个季度的芯片生产预测。Agile Analog的Composa 技术解决了模拟IP在传统上需要重新设计以适应每种不同的硅工艺技术的问题。

“每次使用不同的代工厂时,这种特定于工艺的重新生成 (respin) 都会消耗宝贵的工程工作,而这些工作时间可以更好地专注于增值的差异化设计工作,”Agile Analog产品营销副总裁Barry Paterson解释说。“当客户将我们的模拟IP核集成到他们的设计中时,我们可以使用PDK自动生成,适应于每种不同的硅工艺技术新版本的IP。

能够访问任何工艺技术的能力也有助于客户迁移到通常位于较小工艺节点上的下一代产品系列。大多数增强功能通常发生在数字实现中,而提供基础模拟功能、数据转换和电源转换的模拟IP通常保持不变。保持模拟IP性能和功能,同时由Agile Analog为较小的工艺节点重新生成,使客户能够将其宝贵的模拟设计工程师集中在创新和差异化的设计工作上,而不必处理所有模拟电路。

关于 Agile Analog Ltd.

模拟 IP 对于每个设计都需要不同。这就是为什么Agile Analog 创造了一种新的做事方式,由业内一些最优秀的人才构思。我们提供各种模拟 IP,可根据您的需求快速定制,在任何半导体工艺上都能实现更高的质量。请通过 www.agileanalog.com 与我们联系以了解更多信息。