Sondrel正在改变

可测性设计(DFT)本质上是设计过程中的一个步骤,在这个过程中测试功能会被添加到硬件里。虽然这些功能对性能提升来说不是必须的,但作为测试制造过程的关键一步,它们确保了芯片在产品中能够正常运行。

DFT有许多好处,对设计和制造过程尤为如此。其中第一个也是最重要的是,任何复杂的设计都需要可测试性,而有效的DFT则可以在全面测试和运行这些测试所需的时间之间取得平衡。

测试需求

早期,可以通过相对较少的测试规划对带有几个电闸的简单电路进行试验,而现代的应用型专用集成电路(ASIC)不但物理尺寸较大,还比以前的简单电路更加复杂,且随着时间的推移,这种复杂性还会逐步增大。随着电路变得越来越复杂,在设计实现后创建有效的测试程序变得更具挑战性、更耗时,专业性要求也更高了。从必要性来说,将可测试性的想法纳入设计流程是不可避免的一步,所以DFT已经变得无处不在了。

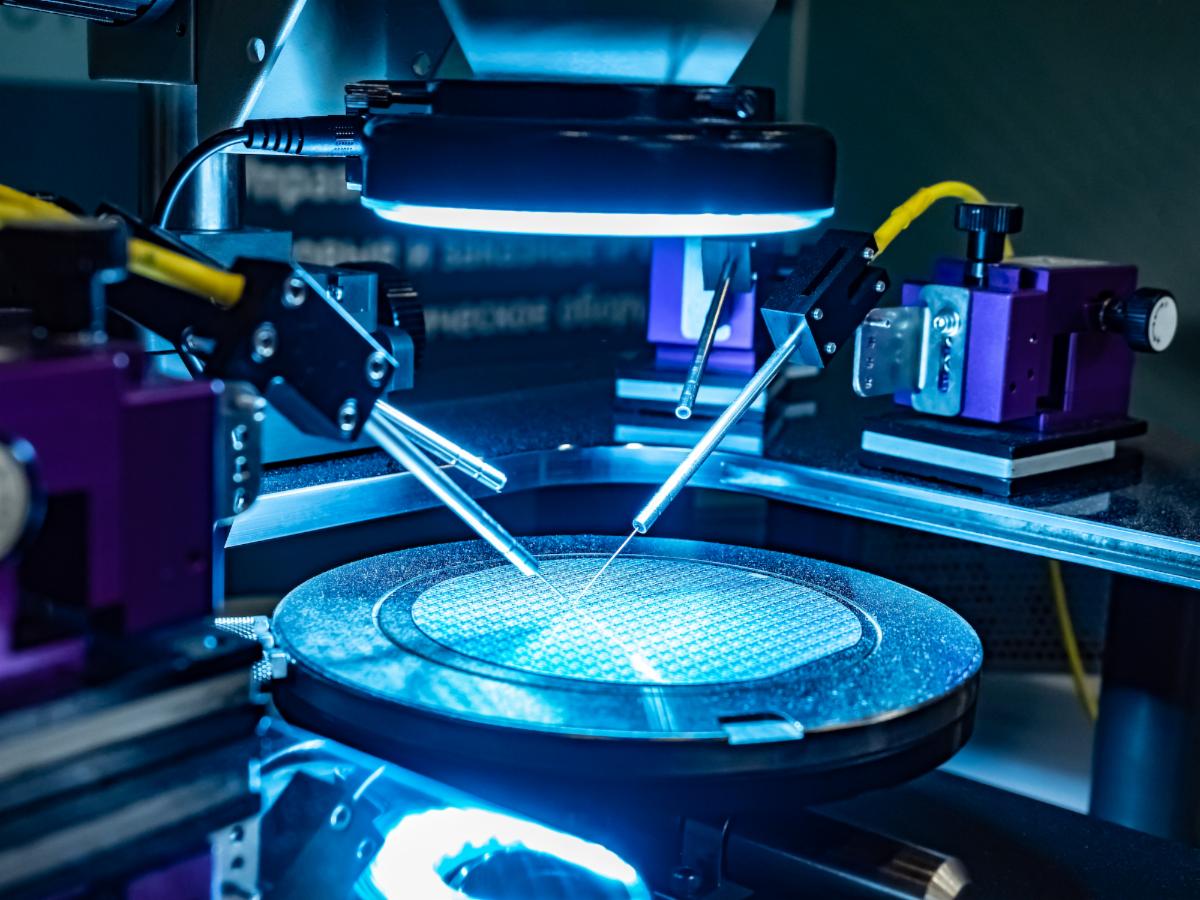

当考虑到人造硅的潜在缺陷时,进行过可靠测试然后生产的芯片是确保交付给客户的产品性能达到预期标准的一个重要步骤。精心设计的DFT元件将实现这一点,同时最大限度地减少逻辑测试所占用的额外空间和硅。测试程序不仅可以确定某个芯片是否出现故障,还可以提供足够的细节以预测将会出现缺陷的地方。

测试时间

人们已经清楚地了解到了硅制造的缺陷,而且由于在更复杂的设计中使用了更先进的技术,错误出现的可能性也变高了。总有一些存在缺陷的芯片令人不满意,甚至根本无法使用。因此,测试是确保最终产品质量的重要步骤。

然而,测试所有芯片是一项耗时的任务。并且和其他任何任务一样,这种测试也是有成本的。也许测试只需要几秒钟,但如果把时间与芯片数相乘,花在测试上的每一秒钟都必须是独具意义的。因此,利用专门添加到设计中的逻辑测试,人们可将测试程序的时间大大缩短,从而节省大量测试成本。

然而,DFT工程师还必须考虑运行测试功能所花费的时间。一个完美的设计会在具体细节上识别和诊断每一个可能的缺陷,但这不仅可能会占用更大的空间,还会增加测试时间,所以不具备商业可行性。最终,我们需要达成一种微妙的平衡,那就是既要充分透彻检测设计,又不能过于深入而导致财务上的限制。

那么,DFT包含哪些内容呢?

既然我们已经明确了DFT的必要性,那DFT中又包含了哪些内容呢?首先我们必须了解ASIC或者其中的一部分电路设计目的是什么,设计师又采用什么方法来达到这一目的。一旦本标准以及其他任何适当标准建立,就可依据其复杂性与要求确定设计方法。

而所涉及DFT的内容也不尽相同。有些技术是相对容易实现的,例如在设计中引入额外复位,可以帮助设计更快进入已知状态,方便进行测试。然而,这些技术却阻碍了人们去实施更宏大的策略。更常见的技术可能包括基于扫描的测试、内置自检或联合测试工作组(JTAG)支持,以更多观察电路表现方式,从而获得更多信息来确定故障性质。

应该在什么时候开展DFT?

和任何设计的特点一样,有效的DFT设计需要在ASIC架构早期迭代起始时就采用适当策略,避免后期的重大调整。尽管通常DFT大部分是在流程后期插入设计中的,DFT工程师也有可能在寄存器传输级设计阶段时就进行深入分析,从而识别可能经证明为有用或有害的元素。一旦设计架构和寄存器传输级基本建立并得到验证,DFT工程师就可通过设计融入他们认为最合适的技术,而不必担心系统出现重大变化。由于DFT必须引入一定程度的附加逻辑,物理设计工程师也需在流程早期充分领会DFT计划,以便将其纳入布图规划中。

当代工厂收到设计时,它将能够快速有效地测试所生产的硅芯片,通过有效应用DFT来平衡测试的透彻性、速度和信息,从而获得最大收益。

关于Sondrel

Sondrel成立于2002年,是集成电路各阶段设计方面值得信赖的合作伙伴。其在定义和设计专用集成电路方面的咨询能力屡获殊荣,为其将设计转化为经过测试的批量封装硅芯片的专用集成电路一站式服务提供了有力补充。整个供应链流程的单点联系,确保风险低,上市时间快。Sondrel总部位于英国,其通过在中国、印度、法国、摩洛哥和北美的办事处,为全球客户提供支持。更多信息,请访问www.sondrel.com