降低半导体金属线电阻的沉积和刻蚀技术

使用SEMulator3D®可视性沉积和刻蚀功能研究金属线制造工艺,实现电阻的大幅降低

大面积分析技术可以预防、探测和修复热点,从而将系统性、随机性和参数缺陷数量降至最低,并最终提高良率

SEMulator3D 工艺建模在开发早期识别工艺和设计问题,减少了开发延迟、晶圆制造成本和上市时间

使用SEMulator3D®工艺步骤进行刻蚀终点探测

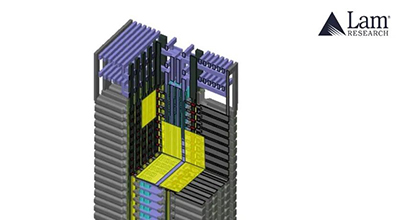

SEMulator3D®虚拟制造平台可以展示下一代半大马士革工艺流程,并使用新掩膜版研究后段器件集成的工艺假设和挑战

SEMulator3D将在半导体器件设计和制造中发挥重要作用

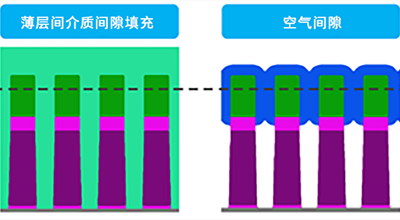

在本文中,我们将论述如何通过在SEMulator3D®中使用可视性刻蚀建模来弥补干法刻蚀这一方面的不足。

在DRAM结构中,电容存储单元的充放电过程直接受晶体管所控制。随着晶体管尺寸缩小接近物理极限,制造变量和微负载效应正逐渐成为限制DRAM性能(和良率)的主要因素。而对于先进的DRAM,晶体管的有源区 (AA) 尺寸和形状则是影响良率和性能的重要因素。在本研究中,我们将为大家呈现,如何利用SEMulator3D研究先进DRAM工艺中存在的AA形状扭曲和与之相关的微负载效应与制造变量。