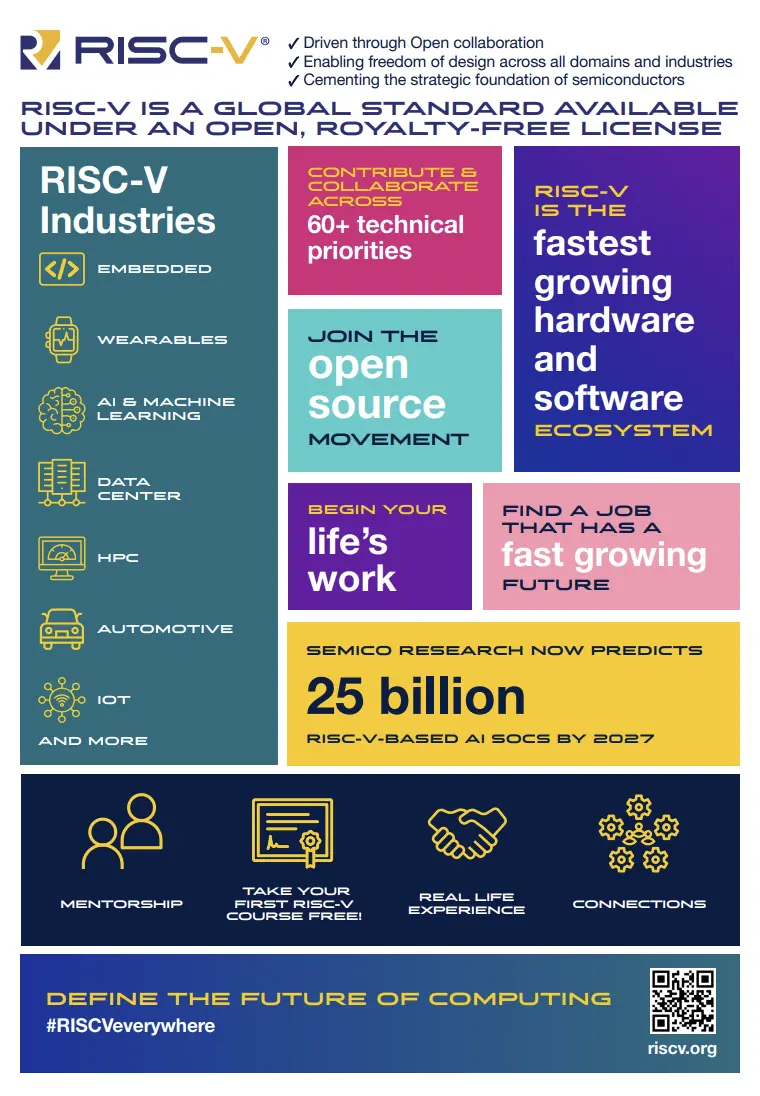

在近日召开的 Embedded World 大会上,RISC-V International 首席执行官 Calista Redmond 高兴地宣布目前 RISC-V 市场上的核心数量已经突破 100 亿。之所以取得这个重要里程碑,Calista Redmond 认为开放标准是关键。她表示:“Linux 在为软件所做的事情,和我们为硬件所做的事情有异曲同工之妙。目前我们预估市场上 RISC-V 核心数量突破了 100 亿”。

RISC-V 是一种开放标准指令集架构 (ISA),根据开源许可提供,可免费使用。基本指令集具有 32 位固定长度自然对齐的指令,并且 ISA 支持可变长度扩展,这意味着每条指令可以是 16 位包内的任何数字长度。

该指令集有 32 位和 64 位地址空间风格,并且是为广泛的用途而创建的。各种子集支持从小型嵌入式系统到 PC 到带有矢量处理器的超级计算机到仓库规模的机架式并行计算机。

通往百亿核心的道路并非坦途。据悉,ARM 架构经过 17 年的反复试验,在 2008 年实现了这个里程碑。而 RISC-V 只用了 12 年就完成了百亿。 Redmond 预计 RISC-V 处理器内核的数量到 2025 年将达到 800 亿个。

伴随着这个重大利好消息,今年还将会部署 4 个新的规范和扩展。四个新规范是:

● SBI 的 RISC-V 规范在 supervisor 模式(S 模式或 VS 模式)下使用应用程序安装接口,在硬件平台和操作系统内核之间构建了一个固件层。

这种抽象支持跨所有 RISC-V 操作系统实现的通用平台服务。许多 RISC-V 成员已经在他们的 RISC-V 解决方案中实施了 RISC-V SBI 规范,因此批准该规范将确保整个 RISC-V 生态系统的标准方法,确保兼容性。本规范的制定和批准由 Rivos 的 Atish Patra 领导,平台水平指导委员会负责开展工作。

● RISC-V UEFI 协议将现有的 UEFI 标准引入 RISC-V 平台。

本规范的开发和批准由 Sunil V L, Ventana Micro 和 Philipp ToMSIch, VRULL GmbH 领导,工作在特权软件技术工作组中进行。

● RISC-V 的 E-Trace 定义了一种使用分支跟踪的高效处理器跟踪方法,非常适合调试从微型嵌入式设计到超强大计算机的任何类型的应用程序。

RISC-V 文档的 E-Trace 指定了 RISC-V 内核和编码器(或入口端口)之间的信号、压缩分支跟踪算法和封装压缩分支跟踪信息的数据包格式。该规范的开发和批准由 Picocom 的 Gajinder Panesar 和 RISC-V 的 E-Trace 任务组领导。

● RISC-V Zmmul Multiply Only 支持需要乘法运算但不需要除法的低成本实现,并且是 RISC-V 非特权规范的一部分。此扩展的开发和批准由 Allen Baum 领导,工作在非特权 ISA 委员会进行。

来源:cnBeta.COM