2022年12月26-27日,中国集成电路设计业2022年会暨厦门集成电路产业创新发展高峰论坛(ICCAD 2022)盛大开幕。

值此行业盛会鸿芯微纳正式发布三大新产品

RocSyn®——版图驱动的逻辑综合工具

ChimeTime®——静态时序签核工具

HesVesPower®——功耗签核工具

新品发布

鸿芯微纳CEO黄小立表示:“鸿芯微纳三大新工具的问世,填补了国产数字EDA相关领域的空白。此前,鸿芯微纳已推出以布线为中心的布局布线工具Aguda®,取得了积极的反馈,得到了市场的认可。如今,四大产品强强联合,正式宣告鸿芯微纳已实现国产数字芯片EDA平台关键节点的技术部署,成为目前国内为数不多拥有完整的数字芯片全流程工具链的企业,将为本土更多芯片设计企业提供更专业全面的解决方案。”

三大新产品初亮相 让我们一起先睹为快吧!

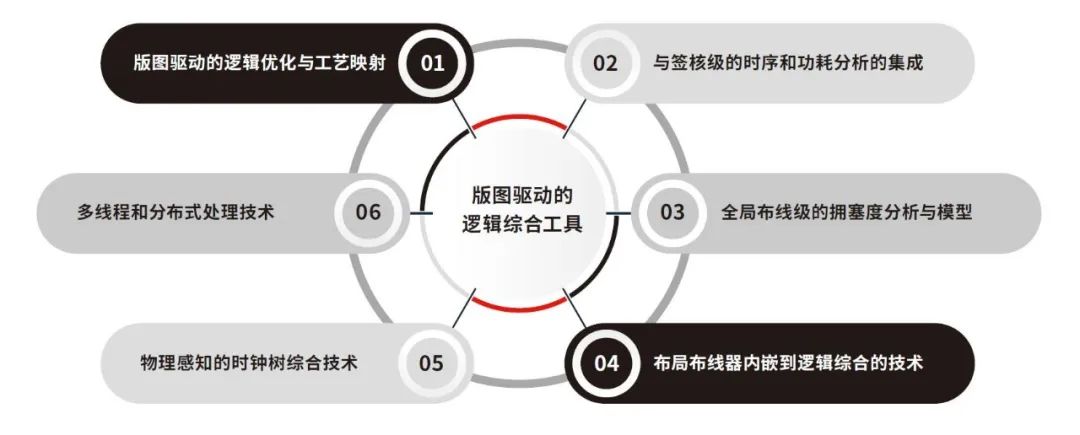

RocSyn®

版图驱动的逻辑综合工具

RocSyn®实现逻辑综合的完整流程:支持Verilog 2005和SystemVerilog 2017标准,支持时序约束(SDC),低功耗设计,UPF综合,扫描链插入,增量编译等功能。

提供多层次、多方位的优化:包括高层次优化,数据链路优化,逻辑优化,基于时序的优化,基于版图的优化等。

性能指标(延时,面积,功耗,即PPA)达到国内领先和国际一流水平。

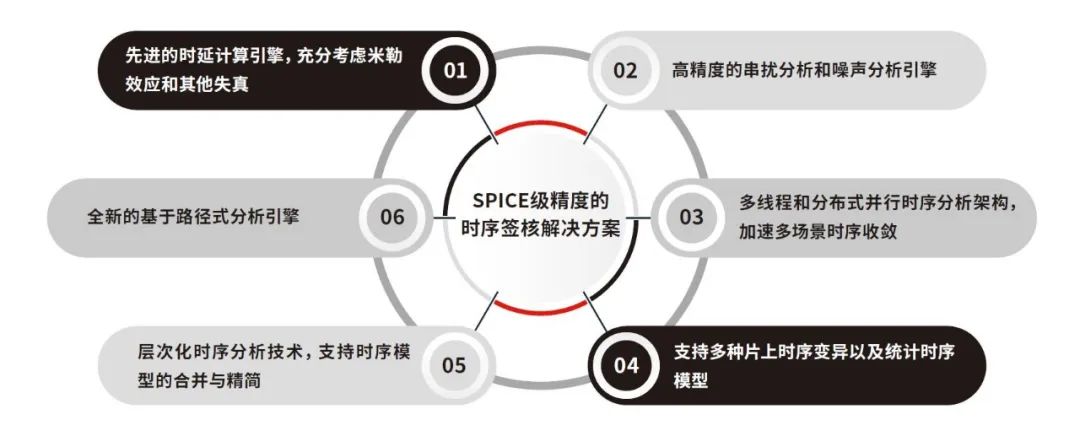

ChimeTime®

静态时序签核工具

ChimeTime®是一种静态时序签核工具,提供了SPICE仿真精度的签核结果。

其搭载了独特的分布式处理能力,可在数百颗CPU上并行运行,快速完成大规模设计的分析。

支持先进的CCS模型,具有针对低功耗设计先进的延迟、串扰计算引擎。

支持各种OCV(包括LVF)格式。支持快速PBA时序分析能力。

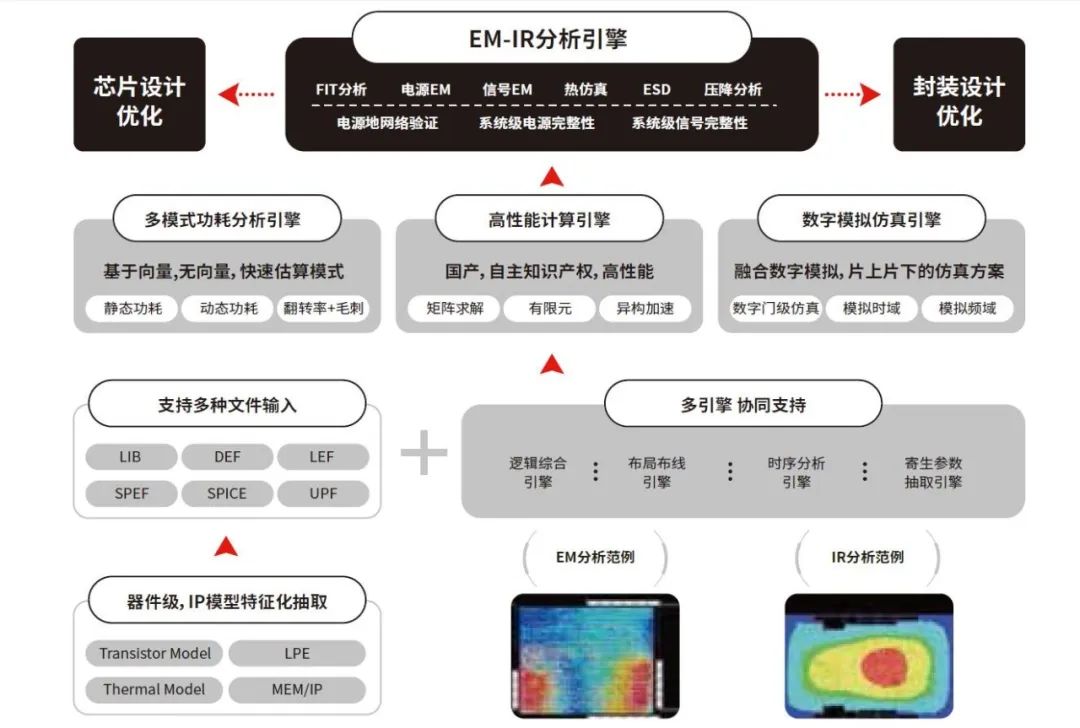

HesVesPower®

功耗签核工具

HesVesPower®,对全芯片系统进行功耗,电源和信号完整性分析以及相关模型抽取,是数字后端实现和系统集成之间的关键签核步骤。

具备自主知识产权的高性能求解器,分布式计算架构,和多物理模型仿真引擎。

◇ 主流功能:功耗压降电迁移分析

◇ 扩展功能:从器件到系统级的功耗签核流程

◇ 核心功能:高性能计算引擎

关于鸿芯微纳

深圳鸿芯微纳技术有限公司成立于2018 年,是一家致力于国产数字芯片电子设计自动化(EDA)研发、生产和销售的高科技公司。旨在通过自主研发、技术引进、合作开发等模式,完成数字EDA关键节点的技术部署,打造完整的国产数字芯片全流程工具链,实现产业链的技术突破;企业依托国内完整的产业生态,组建专业的研发和支持团队,建设具有竞争力的技术平台,致力于在广阔的应用领域,为全球芯片设计业提供全方位的解决方案和技术服务。

公司在深圳、上海、北京和成都的研发中心集中了海内外的优秀人才,均来自于国际知名的EDA和设计公司,人均10年研发经验。通过独立完成复杂项目的流片,获得了国内先进设计公司在内的商业客户的认可。