探讨晶圆背面的半导体新机遇

作者:

泛林集团 Semiverse™ Solutions半导体和工艺整合工程师 Sandy Wen

原文链接:

https://www.coventor.com/blog/latest-developments-backside-power-delivery/

在我从事半导体设备的职业生涯之初,晶圆背面是个麻烦问题。当时发生了一件令我记忆深刻的事:在晶圆传送的过程中,几片晶圆从机器人刀片上飞了出来。收拾完残局后,我们想到,可以在晶圆背面沉积各种薄膜,从而降低其摩擦系数。放慢晶圆传送速度帮助我们解决了这个问题,但我们的客户经理不太高兴,因为他们不得不向客户解释由此导致的产量减少的原因。

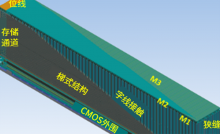

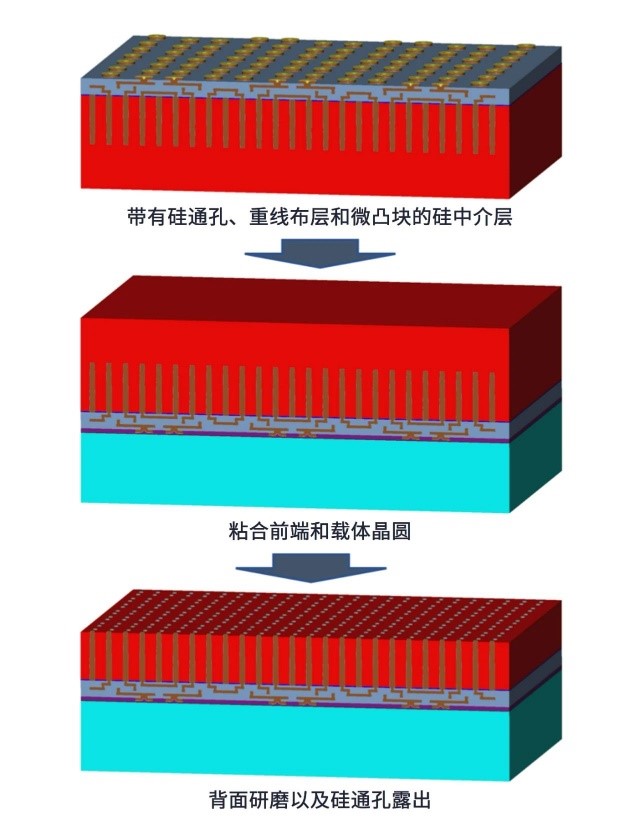

尽管初识晶圆背面的过程不太顺利,但当2010年代早期Xilinx Virtex-7系列FPGA发布时,我开始更加关注这个领域。Xilinx的产品是首批采用“堆叠硅互连技术”的异构集成的FPGA[1]。该技术使用了在不同的FPGA组件之间传递电信号或电力的硅中介层,这一中介层通过创建部分通过硅晶圆的硅通孔 (TSV) 并在顶部创建信号重布线层而成形。通过对晶圆背面进行工艺处理,连接硅通孔的两端:晶圆的正面暂时粘到一个载体晶圆上,然后倒置硅中介层进行工艺处理,随后使用背面研磨和刻蚀来暴露硅通孔。Xilinx产品推出时,我已经离开这个行业,回到了研究生院。在课堂上,硅通孔的金属化是个热门话题,而随着异构集成不断发展,晶圆背面也在工程师中成为了更有意思的话题。

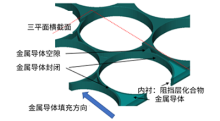

图1:硅中介层的工艺处理。通孔和初始金属化之后,研磨晶圆背面直至到达通孔

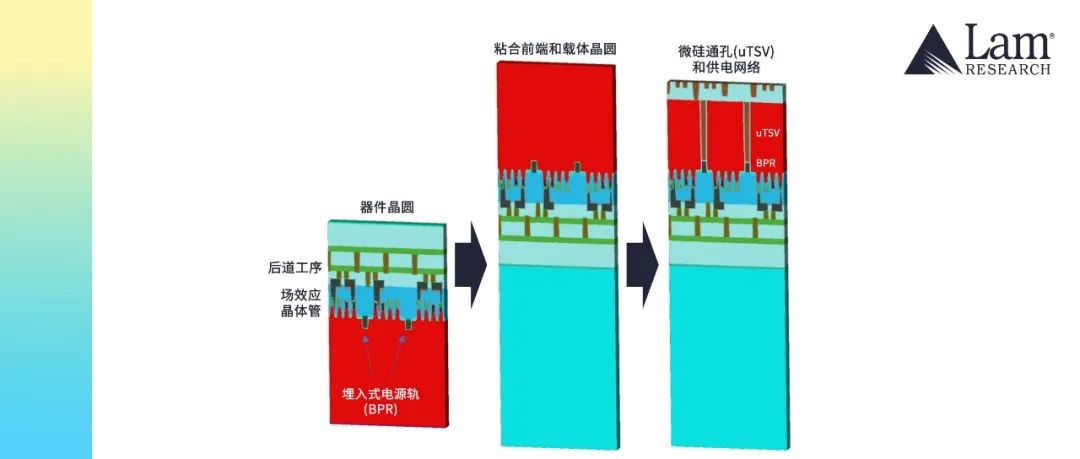

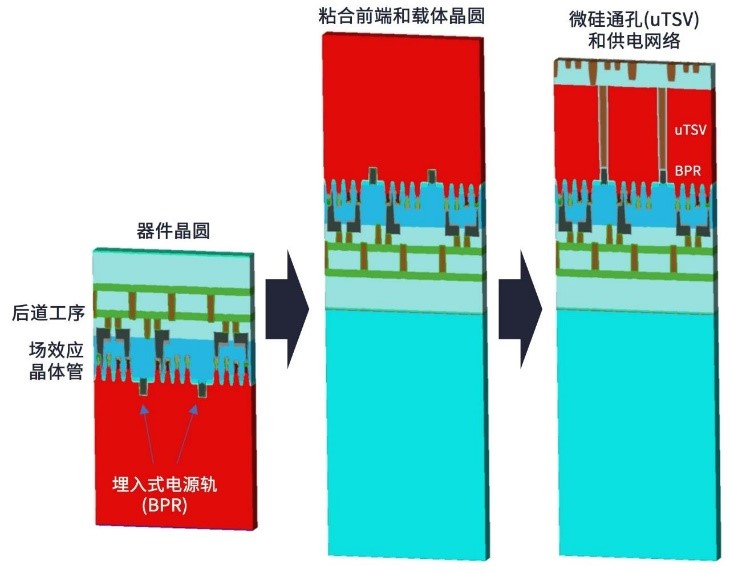

虽然Xilinx FPGA使用了硅中介层来处理信号传输和带宽要求,但去除中介层、直接使用晶圆背面进行电气布线的做法会更有前瞻性。背面供电是“背面”架构的示例之一,它的供电不是来源于传统的晶圆正面的后道工序,而是背面。这种架构可能可以减少电源轨和有源器件之间的电压降。作为背面架构的示例,imec正尝试在鳍片架构中使用埋入式电源轨[2]。在imec的工艺流程中,导轨位于鳍片之间,类似DRAM(动态随机存取存储器)埋入式字线。为了信号传输建成后道工序后,在器件晶圆的背面创建硅通孔,连通埋入式导轨。为了供电也可以在背面进行进一步的互连。

图2:参考资料[2],使用埋入式电源轨进行背面供电(不按比例)

至少出于性能原因,器件晶圆背面的空间看起来很有发展潜力。把电源轨从前端移到背面可以缓解晶圆正面的拥塞,实现单元微缩并减少电压降。领先的半导体逻辑企业深知背面供电的优势,正积极开发背面分布网络。2021年年中,英特尔宣布将使用公司的“PowerVia”技术进行晶背供电;台积电也计划在他们下一节点的技术中使用埋入式电源轨[3]。我们期待看到晶圆背面的未来发展。

参考资料:

[1] K. Saban. “Xilinx Stacked Silicon Interconnect Technology Delivers Breakthrough FPGA Capacity, Bandwidth, and Power Efficiency”, Xilinx WP380, 2012.

[2] J. Ryckaert et al., “Extending the roadmap beyond 3nm through system scaling boosters: A case study on Buried Power Rail and Backside Power Delivery,” 2019 Electron Devices Technology and Manufacturing Conference (EDTM), 2019, pp. 50-52, doi: 10.1109 / EDTM. 2019. 8731234.

[3] D. O’Laughlin, “Backside Power Delivery and Bold Bets at Intel”, https://www.fabricatedknowledge.com/p/backside-power-delivery-and-bold