图腾柱功率因数校正电路一直停留在想法阶段,人们不断寻找它的有效实施技术。现在,人们发现,SiC FET是能让该拓扑发挥最大优势的理想开关。

博客

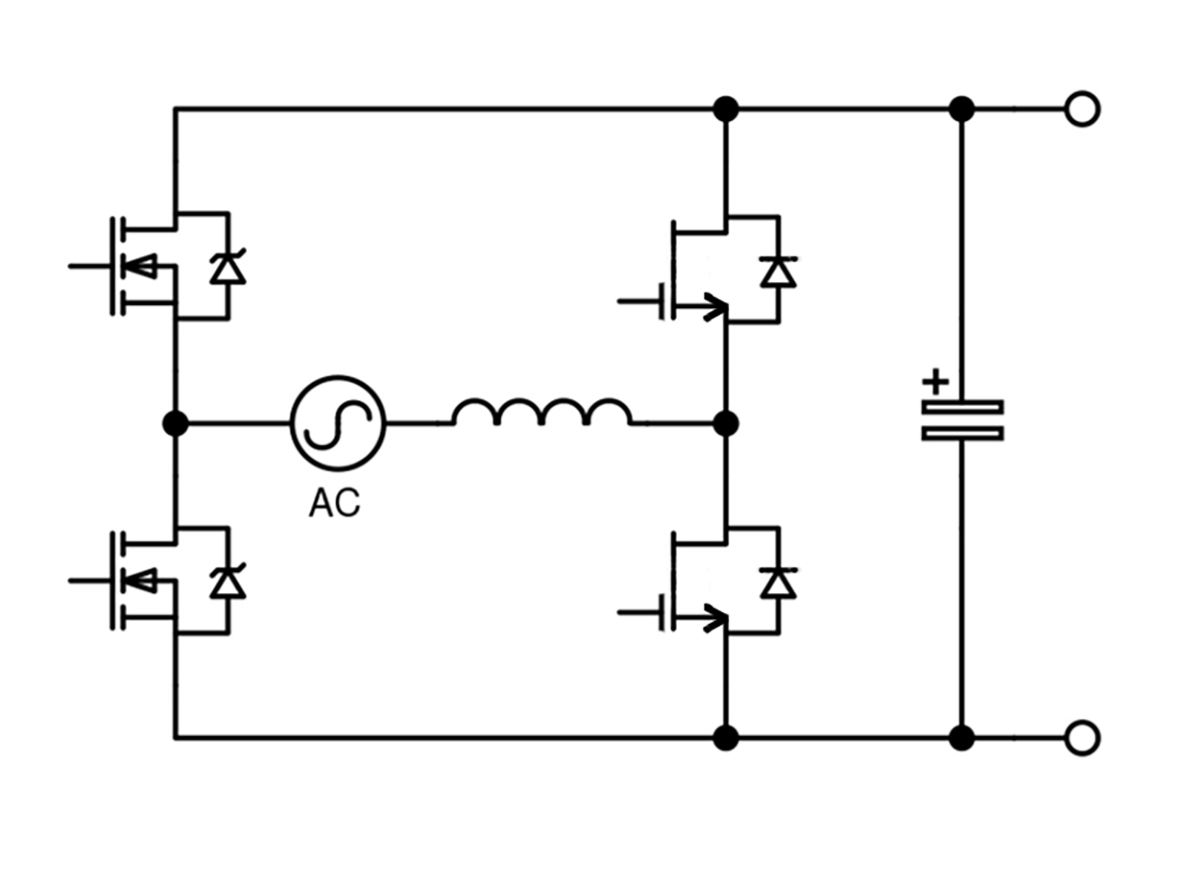

互联网不知道谁首先发明了“无桥图腾柱功率因数校正级”这个术语,但是它肯定是在一瞬间的奇思妙想和灵感下发明和命名的。在交流/直流电源中,该电路会实施功率因数校正,而且由于无需线路交流桥式整流器,可有效提高效率,低压线路可提高2%。下面,我们深入研究,并将其简称为“TPPFC”。

需要理想开关

TPPFC结构于2011年首次得到证实,借助理想开关和低损耗磁性元件,该电路理论上可以实现接近100%的效率。它在流行起来之前只是一个想法,因为直至最近,用于高频升压开关的半导体都还“不够理想”。问题在于在导电损耗与开关损耗之间权衡。要实现更低的导通电阻和导电损耗,就需要更大的有效晶粒面积,但是这会导致器件电容更高,动态损耗更高。还有一个问题,那就是TPPFC必须在“硬开关”持续导电模式和中等及以上功率电平下运行,才能保持峰值电流可控,而且这需要恢复开关体二极管中存储的电荷。当使用硅MOSFET时,电荷足够高,且会导致损耗高到足以让电路不会有任何微小的净收益,尤其是在考虑了开关驱动和控制的成本与复杂性后。

我们正在利用宽带隙半导体实现目标

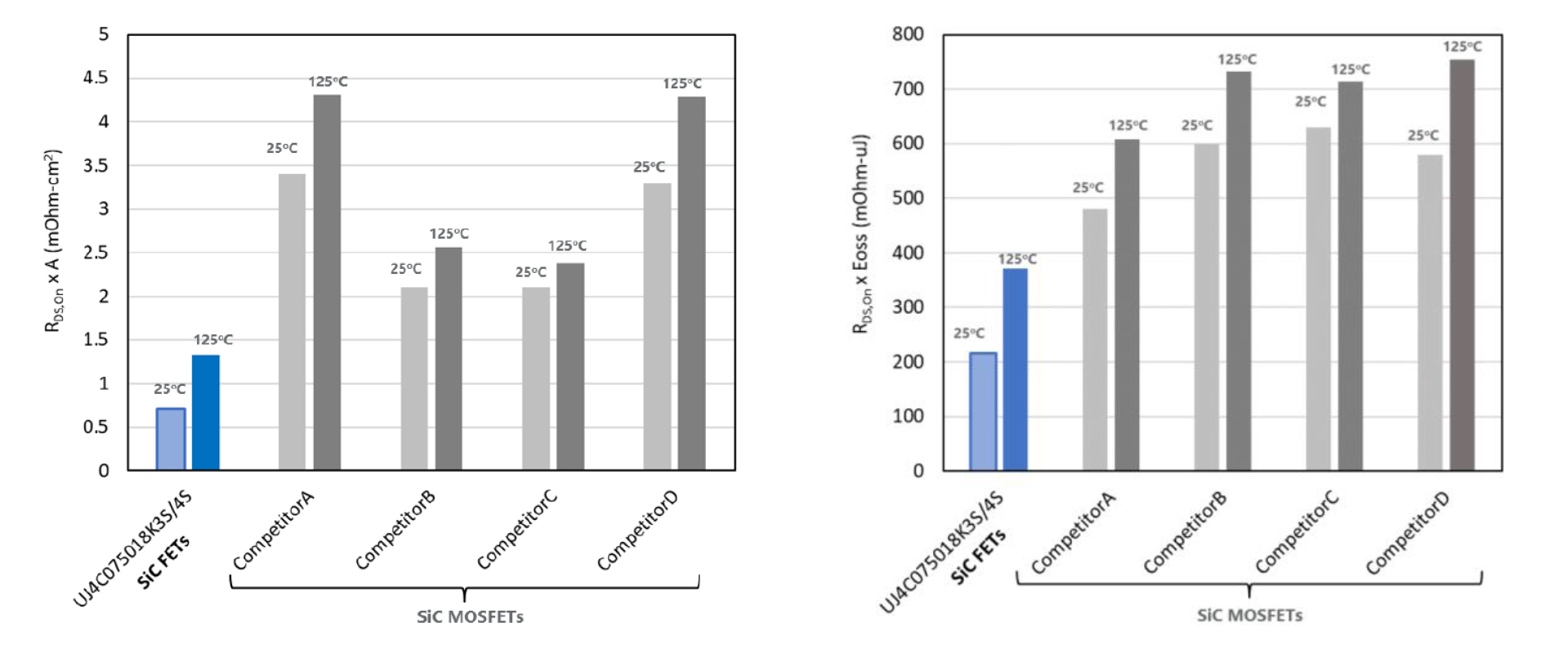

虽然2%的理论效率提高已经很有吸引力了,但是“80+钛金”等服务器效率标准要求在230V交流电和50%负载下交流/直流电源的端到端总损耗要低到4%。因为通常2%要分配给交流前端,所以必须用新技术再次处理TPPFC,以提升它的性能,而宽带隙开关改变了局面。碳化硅和氮化镓都是备选的新技术。相比硅,SiC MOSFET将反向恢复降低了80%,GaN没有反向恢复。它们的输出电容也都比硅MOSFET低,因为在相同电压级下,宽带隙晶粒通常都比硅小。这是因为宽带隙材料的临界电场更高,处理相同峰值电压所需的电压支撑区域薄得多且掺杂重得多,而且随之而来的导通电阻也更低。SiC和GaN的低损耗优势可以用RDS(on) x A和RDS(on) x EOSS这两个性能表征来概述,第一个表示导通电阻和晶粒面积之间的权衡,第二个表示导通电阻与输出电容造成的开关能量损耗之间的权衡。

宽带隙器件使得TPPFC级成为可能,该电路现在很常见,但是还称不上一枝独秀,因为SiC和GaN的这些突出优势隐藏着一些现实中的实施难点。SiC MOSFET的恢复电荷肯定低,但是体二极管的前向压降非常高,这又增加了损耗。栅极驱动对阈值滞后和变化性也很敏感,而且为实现全面增强而推荐的高压也很危险地接近绝对最大值。相反,GaN器件有低栅极阈值电压,但有发生灾难性虚假打开并伴随开关瞬态的风险。负的关闭驱动电压可以缓解这种情况,但是这会在增强沟道前造成当器件反向导电时压降过大,从而增加损耗。GaN还相对昂贵。

SiC FET尽善尽美

虽然还有一个选项,但是半导体制造商数十年来都以结合高压开关与低压类型以获得导电损耗优势和开关损耗优势的“共源共栅”技术而闻名。在典型的宽带隙产品中,常开型SiC JFET与低压硅MOSFET搭配打造出具有非临界栅极驱动、低损耗体二极管和宽带隙器件所有优势的常关型器件。它由UnitedSiC提供,称为“SiC FET”,可以极快地打开,且晶粒体积极小,可实现低电容和低动态损耗。JFET可以有效设置导电损耗,而且其简单的垂直结构支持低导通电阻,即使采用小体积晶粒也不例外。之前提到的性能表征可以证实这些优势。图1表明了750V SiC FET与650V SiC MOSFET的对比情况。

图1. 在关键性能表征方面SiC FET胜过SiC MOSFET

图腾柱PFC电路中的SiC FET不仅能实现潜在的效率增益,还容易实施。可以说,该拓扑和SiC FET开关的组合是“图腾式”的,象征着可以实现最佳结果。