作者:电子创新网张国斌

近年来,美国政府为了阻遏中国半导体发展,在IC制造和EDA工具、IP领域层层设防围堵,不过即便这样,在政府和资本的助推下,本土EDA产业突飞猛进!12月26日,在本土IC设计产业 年度盛会--中国集成电路设计业2022年会(ICCAD 2022)上,深圳国微芯科技有限公司一口气发布“芯天成”五大系列十四款EDA新品!

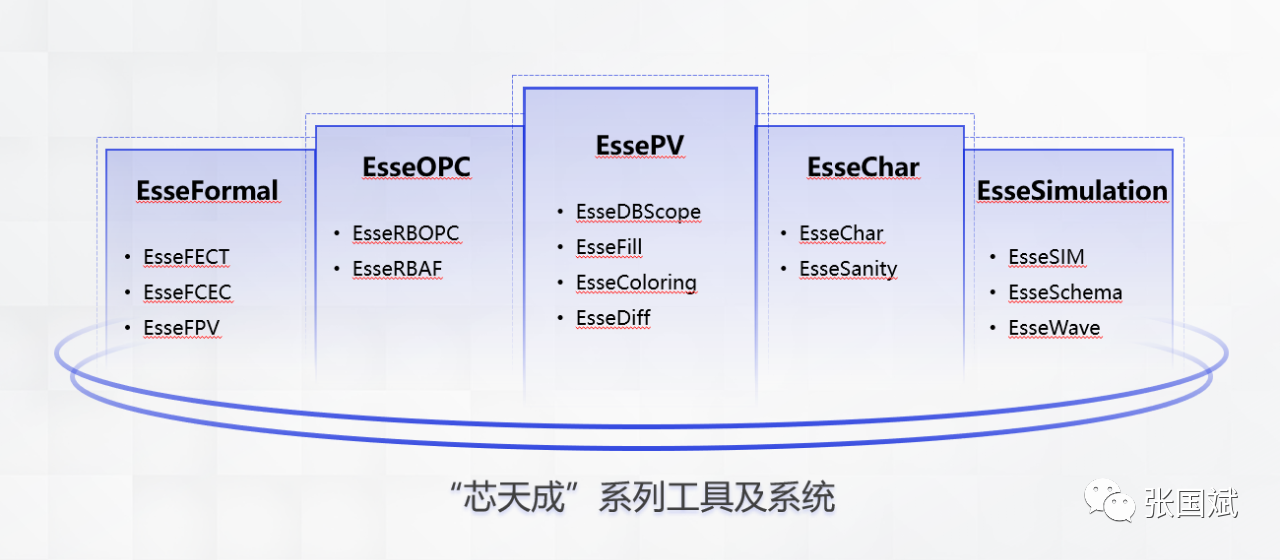

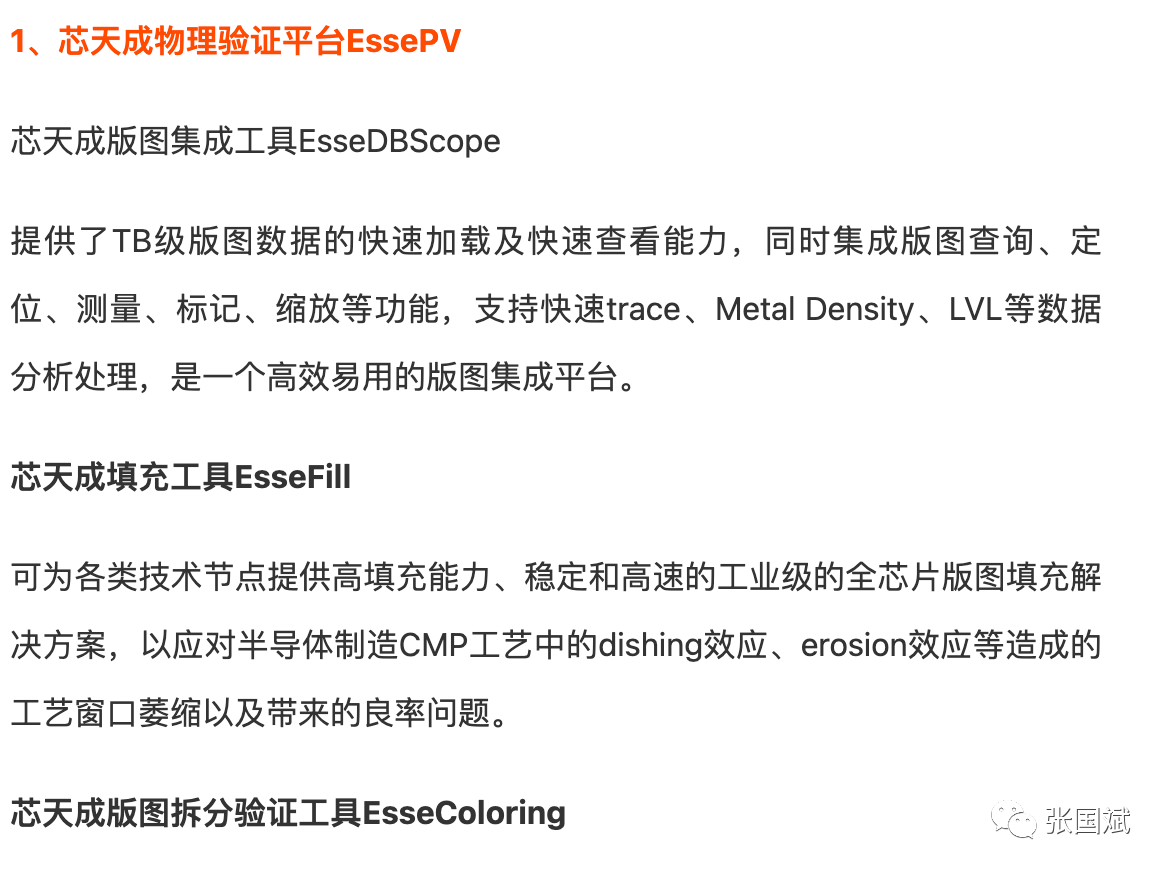

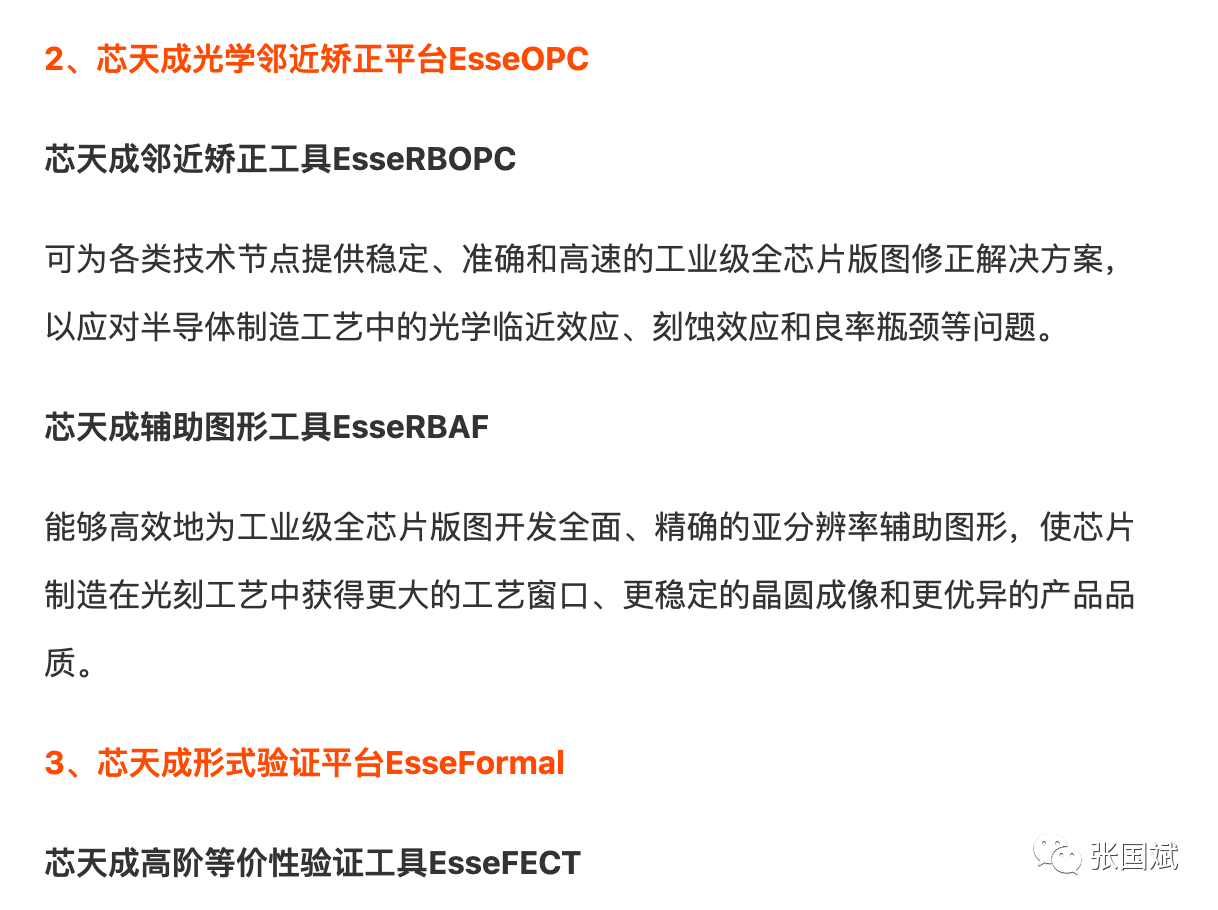

“芯天成”系列五大平台覆盖数字芯片设计后端及制造端,包括物理验证平台EssePV、光学邻近矫正平台EsseOPC、形式验证平台EsseFormal、仿真验证平台EsseSimulation、特征化建模平台EsseChar。

这代表着国产EDA工具已经在部分核心功能及效率上,可与国际领先的成熟产品一较高下,也为我们下一步推出具有国际市场竞争力的数字全流程解决方案打下了扎实基础!

深圳国微芯为何可以一鸣惊人脱颖而出!在ICCAD期间电子创新网等媒体专访了国微芯执行总裁兼首席技术官白耿先生,他分享了国微芯突破的主要原因。

白耿表示国微芯继承国微集团在国产EDA方面的工作和资产,国微2018年承接了科技部的01重大专项,当时国微是主承担单位,有两个共同承担单位,一个是思尔芯,一个是鸿芯微纳,思尔芯负责的是前端验证工具,包括原型验证、硬件仿真、软件仿真;鸿芯微纳负责物理设计端的四个EDA工具开发,包括布局布线、逻辑综合、静态持续、功耗电压降;剩下的形式验证、物理验证、OPC这几个工具本来是在国微集团的EDA事业部,后来分离出来以后,放在了国微芯。

“我们三家的工具开发完全是互补,互相扶持的关系,到现在还是这样,国微芯承接了01专项的物理验证和形式验证成果以后,从2018年做到2020年已经顺利结项了。在01专项里面,物理验证和形式验证没有做产业化的要求,但国微芯把它承接下来,做成产品我们的主要目标。”他解释说,“从2021年开始深圳市发改委又继续在01专项的基础上,对整个全流程的EDA工具进行补链,补链补的是制造端的EDA工具,包括OPC,可制造性、可靠性、良率分析、DFT,这些东西也放在了国微芯的平台上,这就是我们三家的互补关系。”

他表示国微芯的DFT实际上是跟鸿芯微纳的逻辑综合互补,形式验证工具跟前端思尔芯的逻辑综合或者原型工具做等价性验证,国微芯的形式验证能作为支撑。所以三家的工具形成了一条完整的工具链,彼此之间互相互补、互相扶持。

“我们继承了国微承接的政府项目,包括01专项,包括发改委项目,还包括湾区的EDA创新中心项目。这些项目,我比喻前三年是属于政府给一个“奶瓶”,把“小孩子”养大,我们现在经过三年的积累,已经从国微平台剥离出来,现在独立运营,慢慢要变成走市场化道路,现在我们把所有政府承接的项目做成产品,推向市场。”他总结说。“国微芯主要业务是在后端和制造端的国产EDA工具开发上,主要旗舰工具是物理验证工具和OBC工具,OBC工具是给光刻机用的,是光刻机的“心脏”,也有其它的可靠性、制造性、能力分析、DFT和形式验证等一系列工具的开发工作。”

“芯天成”系列五大平台特色

白耿表示国微芯在过去的一年里,与国内多所大学,包括华科、东南大学、南科大等,成立了EDA研究院、EDA联合实验室平台,通过2018年国微集团一路以来的国产EDA积累,公司发布了14款EDA工具,包括物理验证平台上的3个工具,OPC平台上的2个工具,还有仿真平台上的4个工具,以及形式验证工具平台上的3个工具。

目前国微芯主要服务标的是国内Foundry厂,28nm平面Foundry线,支持国内Foundry线进行物理验证相关的参考流程和开发工作,国微芯希望能够在当今的国际环境下,解决国内Foundry厂对于制造端EDA工具的“卡脖子”的问题!

“‘芯天成’系列产品重点解决包括大规模版图解析速度慢、内存占用大、影响上层应用速度、版图文件格式复杂等行业痛点;目前我们重点突破的核心EDA工具,已成功在客户端应用,在版图解析速度等多个核心指标上体现出了明显的竞争优势。”他指出。

本次发布的“芯天成”系列产品主要特点如下:

国微芯EsseColoring版图拆分验证工具可根据工艺规则将同一版图层次拆分成双重版图,并可验证拆分后的版图,是16nm及以下的先进工艺中的双重或多重曝光核心技术方案。

芯天成版图比对工具EsseDiff

可为各类工艺节点提供稳定、准确和高速的版图区别验证技术解决方案,以应对芯片设计中的ECO版图改变验证,以及版图修改预期符合验证等需求。

可以对黄金参考模型(C-Model)和Verilog实现做形式化等价验证,以保证两个实现功能完全形式等价,消除由于仿真验证不全面而带来的功能验证风险。

芯天成等价性验证工具EsseFCEC

可为各类技术节点提供稳定、准确和高速的工业级芯片等价性验证方案,以应对芯片设计与验证过程中的面积优化、功耗优化和验证速度瓶颈问题。

芯天成模型检查工具EsseFPV

使用形式化技术验证 SystemVerilog 断言 (SVA) 属性,为用户提供快速的错误检测以及预期设计行为的端到端的验证。

4、芯天成仿真验证平台EsseSimulation

芯天成模拟仿真器EsseSIM

国微芯自主研发的新一代SPICE精准度、大容量、高性能电路仿真工具,以应对今天高度集成的多功能电路设计仿真需要,如post-layout仿真,电路可靠性仿真等,旨在为模拟电路设计、电路单元特征化、混合电路和数字电路模块验证等提供更好的仿真解决方案。

芯天成电路图输入工具EsseSchema

一款国微芯自主开发的电路图设计软件,旨在为用户提供更加清晰快捷的电路设计界面,提供更加直观的参数设置界面和更简洁的模型导入窗口,以提高电路设计效率。

芯天成电路调试工具EsseWave

国微芯自主研发的高性能波形显示系统,支持读取主流商用仿真软件的输出文件,可以快速地载入数据和显示波形,系统具备强大的图形分析、计算、显示和诊断功能。

5、芯天成特征化建模平台EsseChar

芯天成特征化提取工具EsseChar

国微芯自主开发的新一代特征化工具,基于自主高效的负载均衡分布式系统,内嵌高速仿真软件以及机器学习引擎,能快速抽取客户在先进工艺节点所需要的先进模型(包括不同PVT下CCS, LVF, Aging等模型)。SoC设计平台一体化设计,能够快速简便地实现单元库特征化需求,并无缝反馈到时序分析平台,功耗分析平台,可靠性设计平台等,真正实现数字全流程一体化。

芯天成正确性检查工具Esseanity

国微芯自主开发的单元库/IP验证工具,采用现代图形界面以及数据库技术,能快速验证海量单元库。趋势分析,表格分析,异常点检测等功能可以快速定位单元库的潜在问题,帮助加速签核。独创的时序报告分析功能可以快速对比不同条件下时序报告的变化,缩短设计人员响应时间。质量检测,单元库建库一体化设计,能够在同一个窗口管理所有工作,大大提高建库人员和设计人员的协同工作效率。

白耿表示国微芯“芯天成”系列产品重点解决的行业痛点包括大规模版图解析速度慢、内存占用大、影响上层应用速度、版图文件格式复杂、反复读取成为流片前的效率瓶颈。国微芯的版图集成工具:EsseDBScope具有以下优势:支持业界标准版图格式,解析速度可提高一倍,内存占用则缩减为50%左右。同时推出自研数据格式:smDB。解析完标准版图,硬盘上自动生成smDB格式文档,反复读取版图信息直接从smDB中获取,硬盘装载同样的版图信息,smDB提供10~100倍加速。

此外,国微芯物理验证工具采用基于版图分割的软件架构,核心版图搜索引擎和几何运算引擎均无缝支持大规模并行运算。在现代多CPU的硬件环境中(10~1000CPU),我们的物理验证工具将在速度上体现出独特的优势。

还有,国微芯还推出了面向对象的规则描述语言(OOVF),用法简单直观,热点版图图形直接转化为设计规则。PDK规则描述文件长度缩减50%以上。同时具有可扩展性强的优点:提供灵活性的语法描述规则,在用户端针对新的热点图形进行敏捷开发和验证,新的规则可以方便地并入常规规则。结合内部版图可视化图的数据结构,最大地提升并行处理效率。。

另外,他指出国微芯OPC工具提供人工智能(AI)及GPU异构加速技术,对OPC的核心计算模块提供加速。国微芯已经在这一领域,与产业界和学界在国际上技术领先的团队达成了战略合作 和物理验证工具类似,我们的OPC工具也支持异种任务集群的分布式架构(DP)。

下一步国微芯会与制造厂、IC设计公司战略合作伙伴一起,带动云平台设计模式,加速云上EDA生态成熟。云上无限的并行计算资源,是国微芯多种核心工具(物理验证、OPC、特征化等)并行运算潜力最好的验证和应用平台。

他认为EDA公司发展可以分为四个阶段,第一阶段,实现基本功能,从无到有的突破;第二阶段,能够支持芯片的实际设计和制造过程,达到“可用”的水平;第三阶段,能够帮助客户提升良率,并且实现设计制造流程的再优化,从而达到“好用”的水平;第四阶段,EDA 工具体现核心价值,实现多工具协同优化,并且形成较高的技术和生态壁垒及客户依赖度高、替代成本高,DTCO 贯穿设计与制造环节的多点工具,具备DTCO 工具实力的EDA 公司将具备生态壁垒。

他表示对国微芯而言,需要利用自身的技术优势,在2023至2024年,逐步完成重点工具的开发和市场推广,达到第三阶段的水平。同时,通过与战略合作伙伴的通力协作,逐步实现工具协同优化,利用DTCO的理念建立生态壁垒,提高公司的竞争能力。

“现阶段公司的战略重心是建立与国内工艺厂的充分交流与深度合作。从工艺定义初期开始,贯穿于工艺定义的全过程。通过国微芯、工艺制造厂、IC设计公司的各方面研究团队的共同努力,以实现更好的性能-成本追求。用这种模式,完成工艺线对公司后端/制造端工具的认证,完成对平面(28nm及更成熟节点)工艺和FinFet(14nm、7nm)工艺的支持。”他指出,“公司同时会重视建立高效的PE/AE团队,培养团队正向开发参考流程(PDK)的能力。充分利用DTCO的理念,协同工艺厂和芯片设计公司战略合作伙伴,通过工艺目标和芯片设计目标协同优化,降低工艺线开发投入,加速量产,实现芯片产品更快TTM(Time to market),优化PPAY(Performance,Power,Area,Yield),并在工艺定义的过程中形成定制化的设计和制造端EDA工具。”(完)