简介

本文旨在介绍 安森美 (onsemi) 的在线 Elite Power 仿真工具和 PLECS 模型自助生成工具 (SSPMG) 所具有的技术优势,提供有关如何使用在线工具和可用功能的更多详细信息。我们首先介绍一些与 SPICE 和 PLECS 模型有关的基础知识,接下来介绍开关损耗提取技术和寄生效应影响的详细信息,并介绍虚拟开关损耗环境的概念和优势。该虚拟环境还可用来研究系统性能对半导体工艺变化的依赖性。最后,本文详细介绍对软硬开关皆适用的 PLECS 模型以及相关的影响。总结部分阐明了安森美工具比业内其他用于电力电子系统级仿真的工具更精确的原因。

物理和可扩展 SPICE 建模

基于半导体物理学的物理和可扩展 SPICE 建模的引入替代了行为较不准确的SPICE 模型。此类行为模型无法代表复杂的现代功率器件,例如 SiC MOSFET 和 IGBT。安森美的物理 SPICE 模型可捕捉复杂效应,如反向恢复、自发热以及因制造中的工艺技术分布而引起的电气参数变化。首先会生成一个核心可扩展模型,然后通过调整特定的芯片布局和封装参数,为采用相同技术的多个产品生成模型。

以下白皮书介绍了安森美的物理和可扩展建模的详细信息1,2,3,4。这种建模能力是安森美的先进PLECS 建模能力的基石,在后续章节中有详细介绍。

PLECS 基础知识

PLECS 不是基于 SPICE 的电路仿真工具,此类工具重点关注的是电路元件的低级别行为5。而 PLECS 可通过优化的器件模型促进完整系统的建模和仿真,尽可能地提高速度和精度。因此像 SiC MOSFET 这样的功率晶体管被视为简单的开关,经过简单配置后,可以显示与导通和开关转换相关的损耗。PLECS 模型称为“热模型”,包含导通和开关损耗的查找表以及 Cauer 或 Foster 等效网络形式的热链。通常,基于测量的损耗表与制造商提供的数据表一致。在仿真期间,PLECS 使用损耗表通过插值和/或外推的方法,获得电路运行偏置点下的导通和开关损耗。

用于测量开关损耗的双脉冲测试

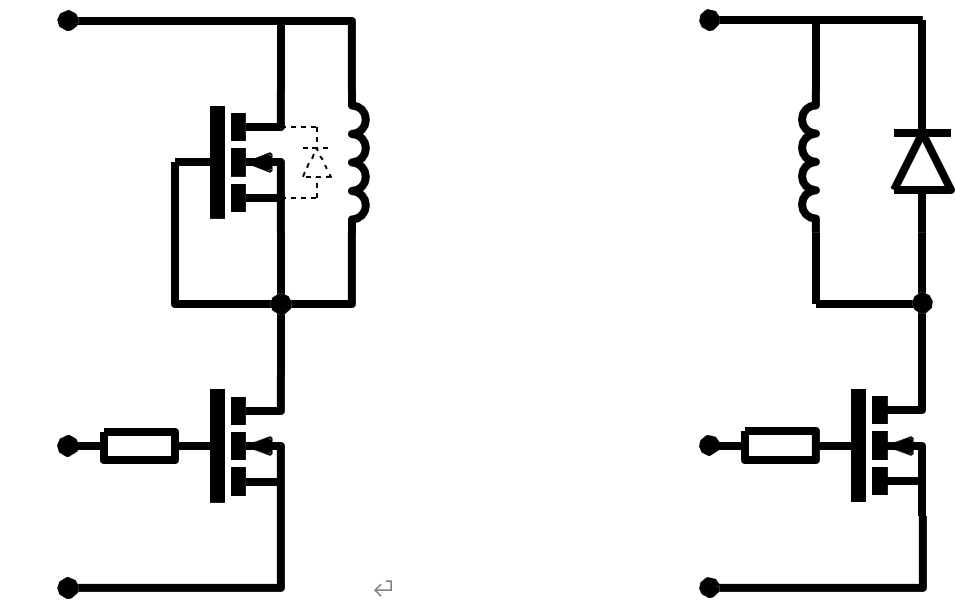

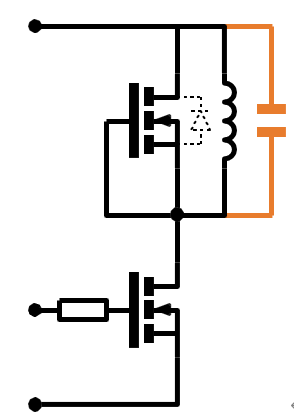

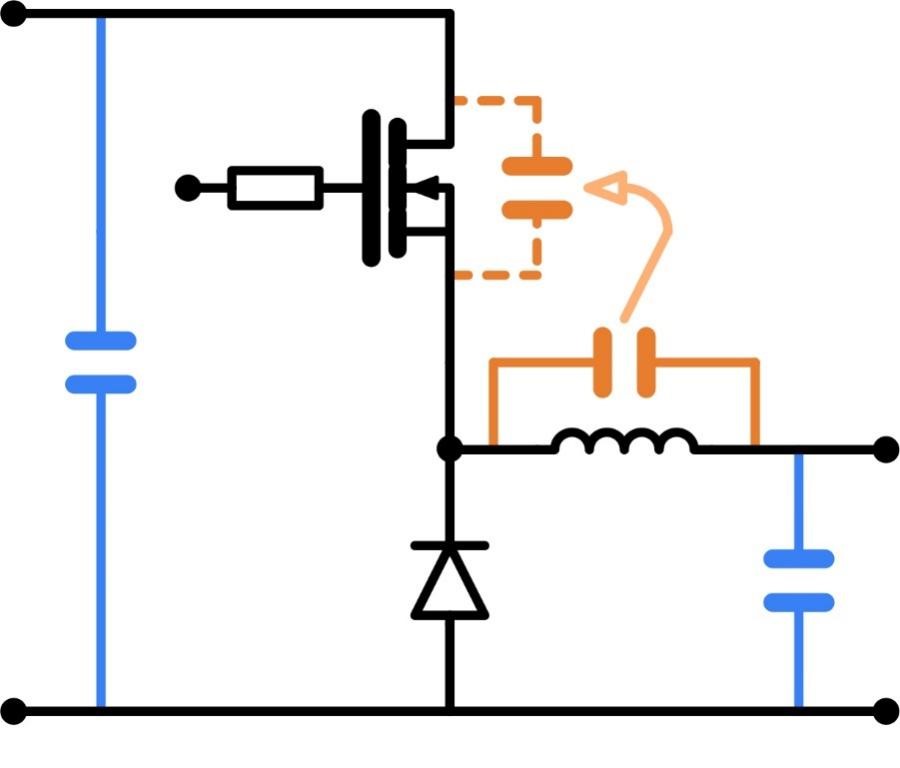

测量开关损耗的一种常用方法是双脉冲测试。理论原理图如图 1 所示。

半桥设置 | 四分之一桥设置 |

图 1.双脉冲测试仪基本原理图

它可以是半桥结构或四分之一桥结构。在测试之初,我们认为电感电流为零,或者说,电感已完全放电。原理如下:

第一步,低边侧开关导通,电感中的电流开始增加。当电感电流达到测量点时,低边侧开关关断。此时,我们测量该电流的关断损耗。然后,在高边侧续流二极管的作用下,电感电流继续流动。由于二极管的压降几乎为零且持续时间很短,因此电感电流在该阶段被视为恒定。最后,低边侧开关再次导通,并使用与前一个关断时刻几乎相同的电感电流测量开通损耗。在此配置中,开关以硬开关方式导通。

我们在白皮书“SiC 仿真”6中提到,双脉冲测试仪的设置方式(半桥或四分之一桥)会影响开关损耗。SiC 肖特基二极管的 QC 远低于 MOSFET 体二极管 QRR。由于高边侧开关/二极管中的该电荷/能量会在低边侧开关导通时耗散,因此相关电路设置(以及外部元件)会影响主开关损耗。此设置可称为“升压”型双脉冲测试。开关电感连接到输入电压。有源开关连接在低边侧。无源开关可以是一个简单的二极管,连接在高边侧。

双脉冲多种可选原理图

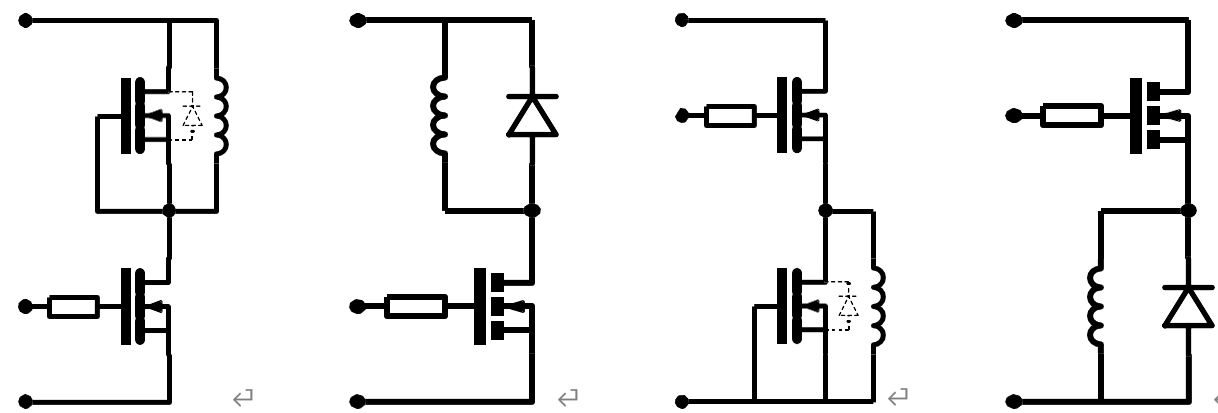

从上一段落中,我们可以通过前面所有的“升压”型双脉冲测试得出“降压”型双脉冲测试电路,如图 2 中所示。

半桥“升压”设置 | 四分之一桥“升压”设置 | 半桥“降压”设置 | 四分之一桥“降压”设置 |

图 2.双脉冲“升压”和“降压”测试原理图

在这种“降压”结构中,更容易看到输出对地短路。有源开关在高边侧,无源开关(也可以是二极管)在低边侧。理论上因为“降压”型与“升压”型相比完全对称,获得的结果应该相同。但实际上因为高边侧开关浮地,“降压”型双脉冲测试需要更复杂的测量设置。众所周知,直接连接或低边侧探针要显著优于差分或高边侧探针。因此,这种设置在现实中很少使用。

寄生效应

在本节中,我们将分析影响有源器件开关损耗的一些主要外部因素。我们已经在白皮书“SiC 仿真”6 中了解了高边侧二极管或 MOSFET 元件的影响。在同一篇白皮书中,我们还可以看到封装或寄生元件的影响。但是 安森美物理和可扩展产品模型已经捕捉封装影响。

电感电容

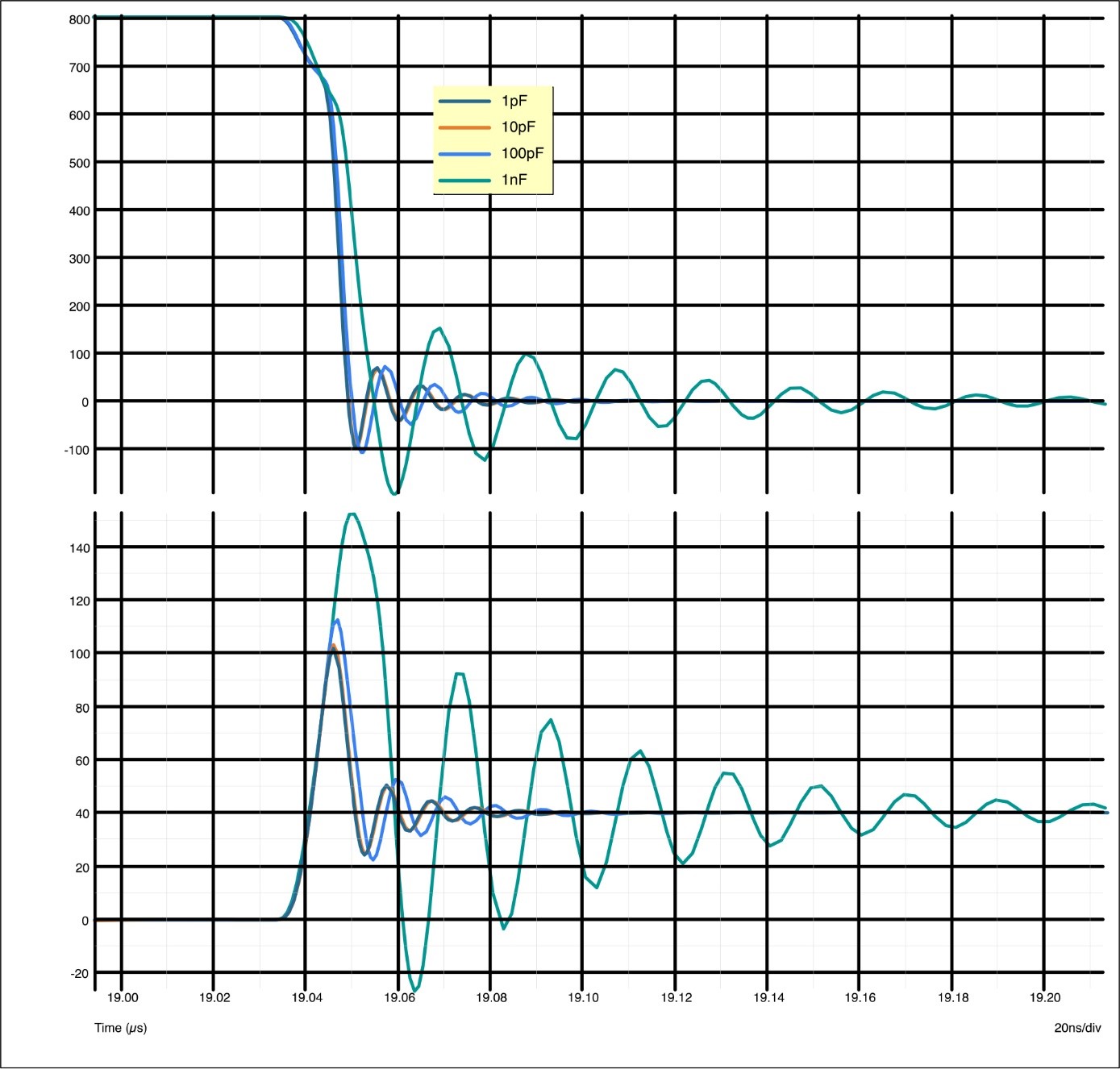

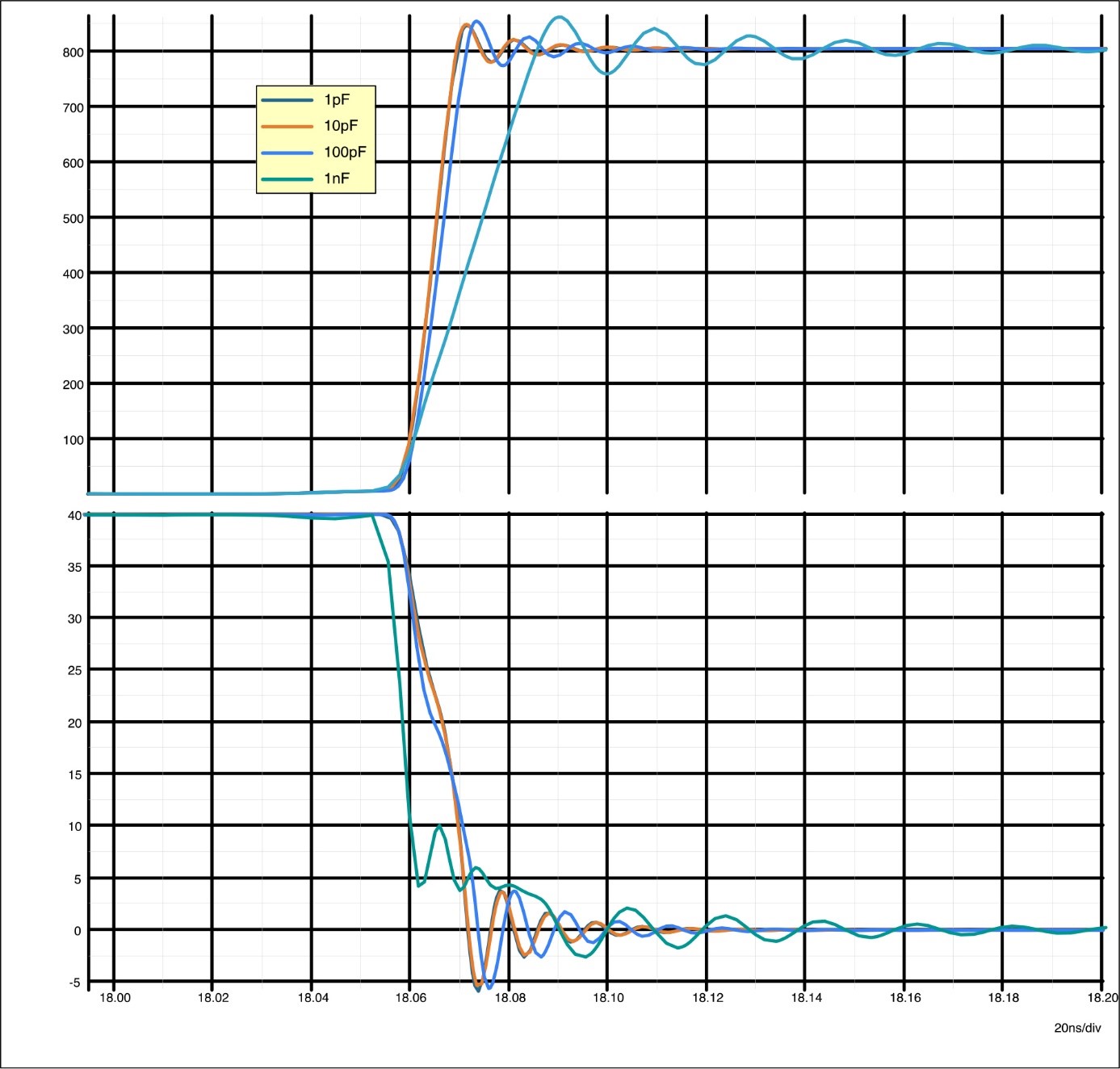

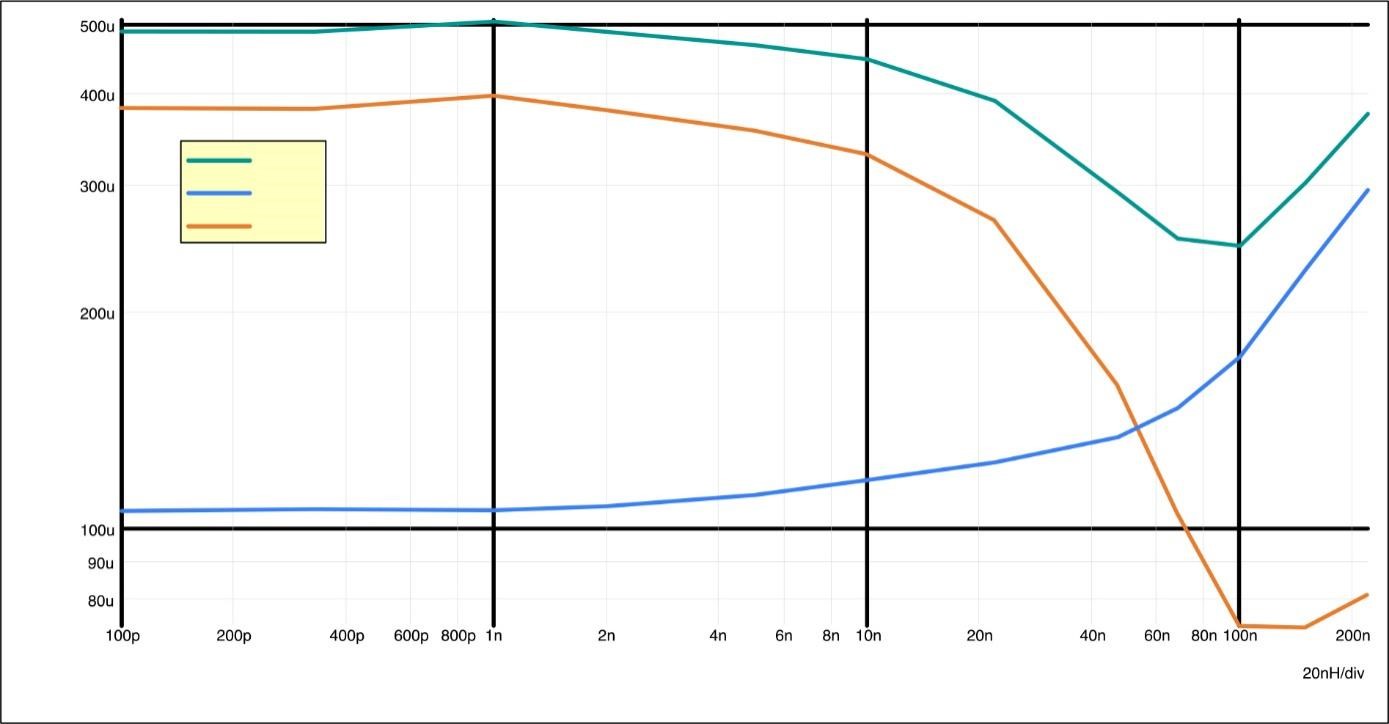

干扰有源开关损耗的第一个元件是开关电感的寄生电容(图 3)。有关其效应的更多详细信息,请参阅白皮书“使用物理和可扩展仿真模型评估参数和应用结果”7。使用下图中的原理图,在几乎理想的双脉冲测试电路中绘制了 Eon、Eoff 与带有 22 mΩ/1200 V M3S SiC MOSFET (NTH4L022N120M3S) 的电感寄生电容的关系图。

图 3.用于仿真双脉冲测试仪损耗的电感寄生电容

带有 10 pF 寄生电容的电感是一个非常好的电感。带有 100 pF 寄生电容的电感是普通电感。最后,带有 1 nF 寄生电容的电感是非常差的电感。图 4 和 5 显示了这种寄生电容对漏极电流和电压上升和下降时间的影响。

图 4.导通时的漏电压和电流取决于开关电感寄生电容值

图 5.关断时的漏电压和电流取决于开关电感寄生电容值

开通时,由于电感寄生电容的作用,大电流尖峰增加。在双脉冲测试中,很容易理解这个寄生电容会增加输出电容 COSS。在关断时,漏电压上升时间随着电容值增加。这是正常现象,因为用固定电流值给较大的电容充电需要更多时间。

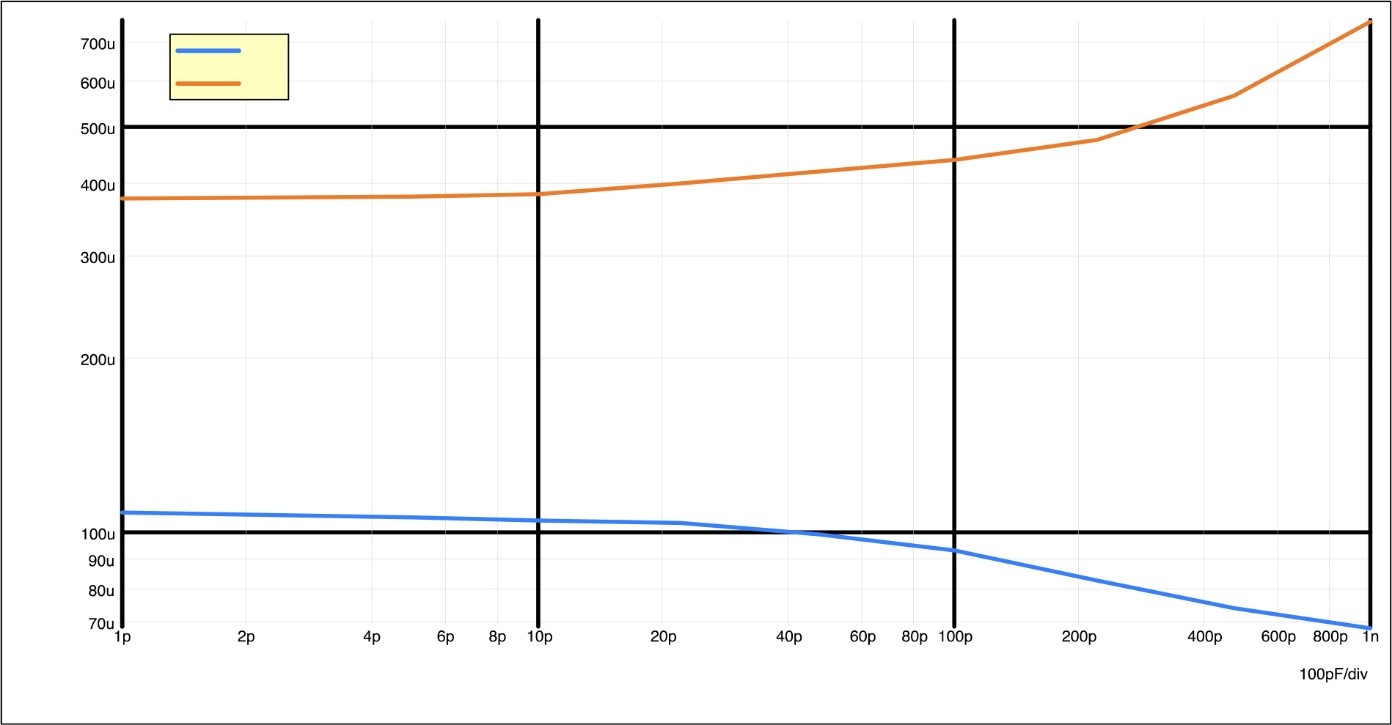

我们可以在下图中看到电感寄生电容对 Eon 损耗的影响。对于非常差的电感,电感寄生电容产生的损耗远高于原生 MOSFET 电容 (COSS)。在图 6 上,我们可以看出差电感造成的 MOSFET Eon 损耗几乎翻倍。

图 6.开关电感寄生电容对导通和关断损耗的影响

在“降压”型电路上也会有一样的结果或效应。考虑到输入和输出端有一个大的去耦电容器,电容(CIN、COUT 和 CParasitic)是串联的。等效电容的值在电感寄生电容的范围内,该值应该更小。该等效电容与 MOSFET 并联,如下一个理论原理图(图 7)中所示。

大型去耦电容

图 7.开关电感寄生电容等效效应

![]()

在较小的紧凑型 DC-DC 转换器中使用平面电感会引起这种现象,因为各层(或匝)以非常小的层间距离堆叠,导致电感的寄生电容较大。在低电压应用中,该寄生电容就已经会带来问题。对于使用 SiC 的高压应用,电感寄生电容的效应会更为显著。

PCB 漏感

我们将在此处讨论的第二个寄生元件是 PCB 漏感。电源设计人员都知道,开关回路越小,性能越好。然而,在某些情况下,为了降低 EMI,可以使用铁氧体磁珠产生一个小延迟来减慢电流上升沿,以便漏电压下降。通过减慢电流斜率以使电压达到“零”也有利于减少损耗。下面的实验使用了一个理想的双脉冲测试电路并在开关回路中添加了可变漏感(参见图8)。其中开关中涉及的各种 PCB 元件之间的距离彼此越来越远,来模拟更大的开关环路

图 8.用于仿真双脉冲测试损耗的布局寄生电感

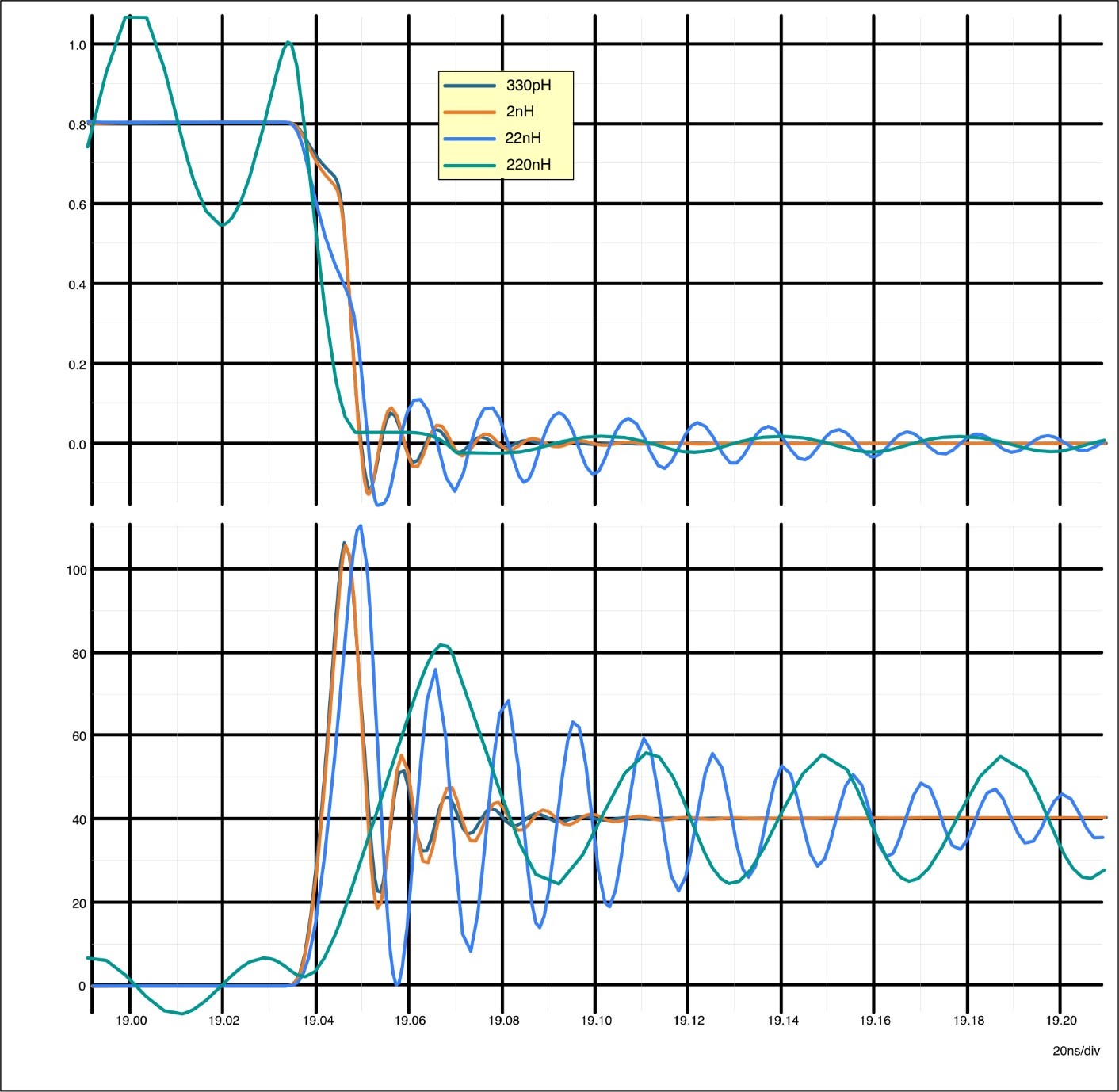

图 9 和 10 显示漏极电流和漏极-源极电压随 PCB 漏感的变化。

图 9.开通时的漏电压和电流取决于布局寄生电感值

图 10.关断时的漏电压和电流取决于布局寄生电感值

在按预期开通时,电压下降斜率 (dV/dt) 相似,而当 PCB 电感增加时,电流斜率 (dI/dt) 变慢。这会造成延迟,因此会像在软开关情况下一样降低 Eon 损耗。关断时,电流下降沿相比电压上升沿延迟,导致更多损耗。图 11 中绘制了开关损耗。

图 11.布局寄生电感对导通和关断损耗的影响

由于 Eoff 通常低于 Eon,是否存在可能降低总损耗 Etotal 的折衷方案?

图 12 绘制开通、关断和总开关损耗与 PCB 漏感的函数关系。

图 12.布局寄生电感对导通、关断和总开关损耗的影响

采用100 nH 寄生电感的总开关损耗似乎有一个“最佳”值。但是,如图 9 和10 中的绿色曲线所示,这个大电感值会引起大的振铃。电流和电压的 EMI 成分很重要,也会影响设计,需要复杂的滤波。由于 EMI 问题总是很难解决,因此难以找到合适的折衷方案。

去耦电容

得益于串联电容网络,与使用电感寄生电容实现的效果一样,去耦电容可以起到相同的作用。在这种情况下,电容应当小并且与电感寄生电容在同一范围内。但是,如果开关电感近乎理想,会发生什么情况?很直观,母线电压会降低。在实际应用中,设计人员需要在去耦电容的数量和母线上的压降之间找到一个折衷方案。此折衷方案应力求尽量减少对损耗的影响。

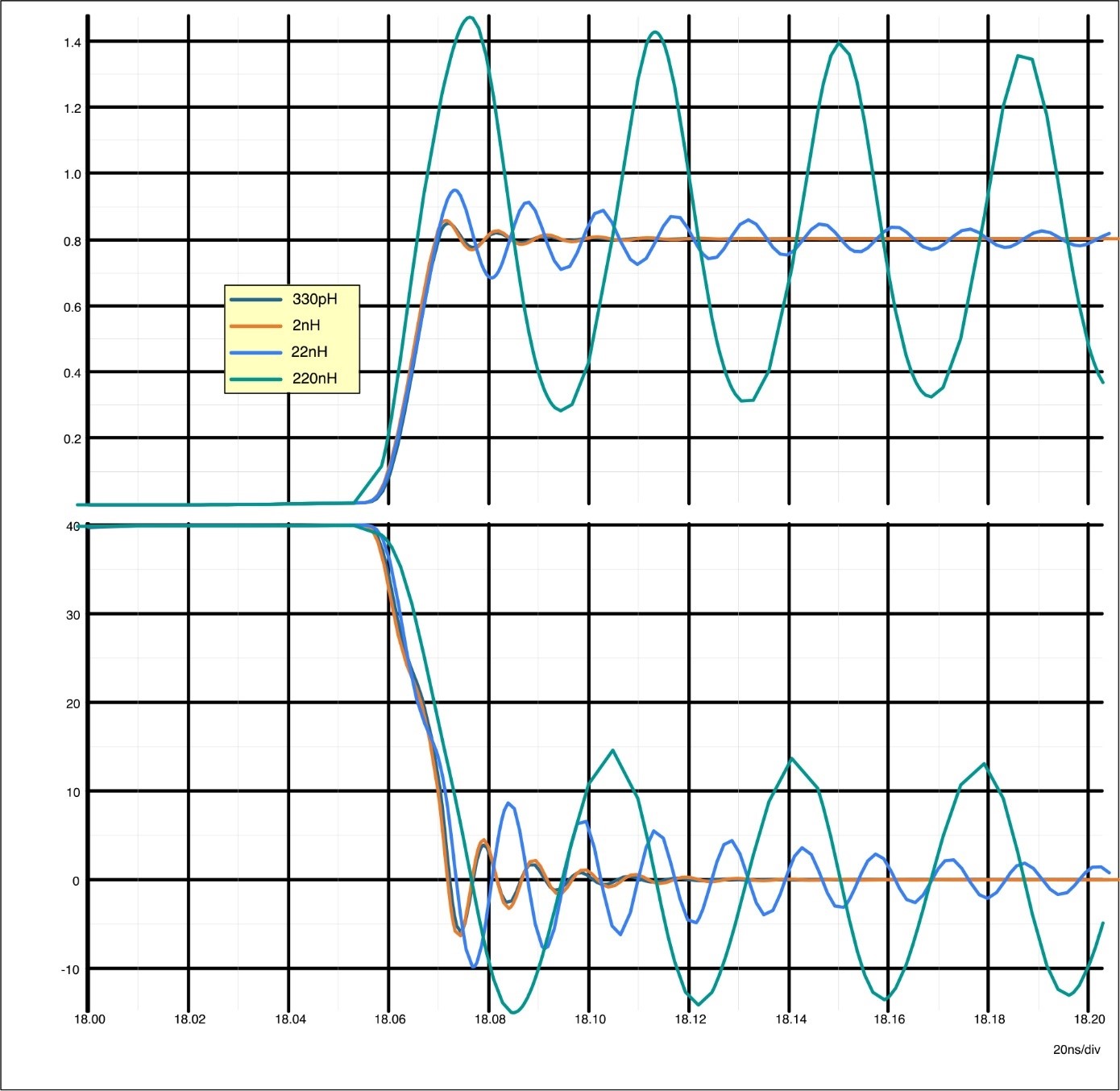

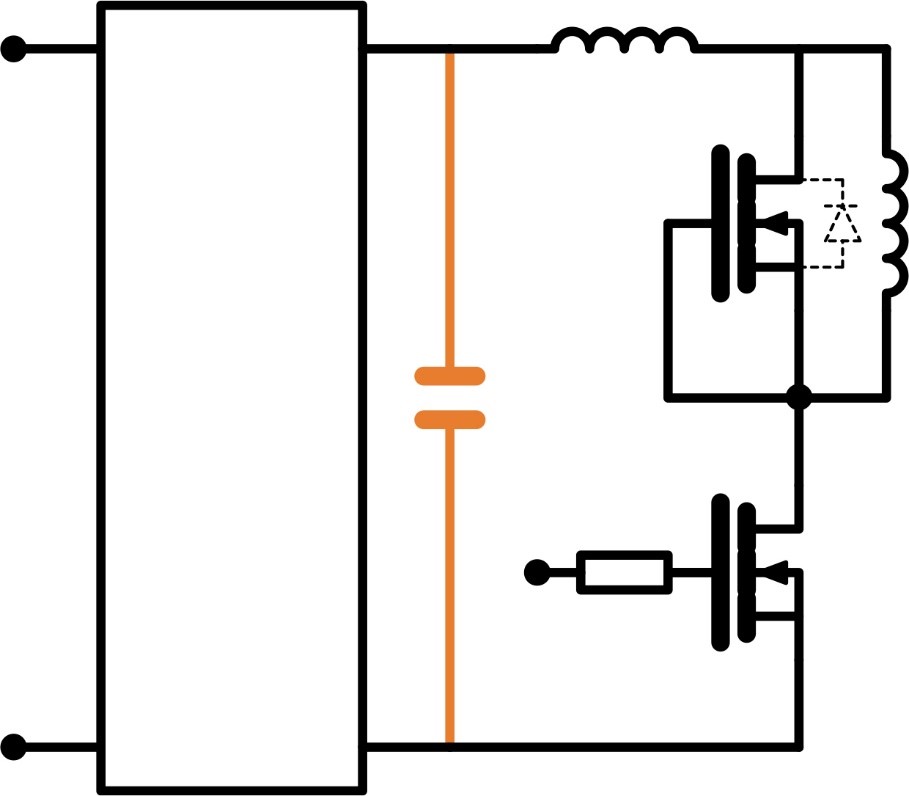

通过配置相同的双脉冲测试电路并包括具有不同去耦电容的输入滤波器来评估对损耗的影响。(参见图 13)

图 13.用于仿真双脉冲测试仪损耗的去耦电容器和输入滤波器

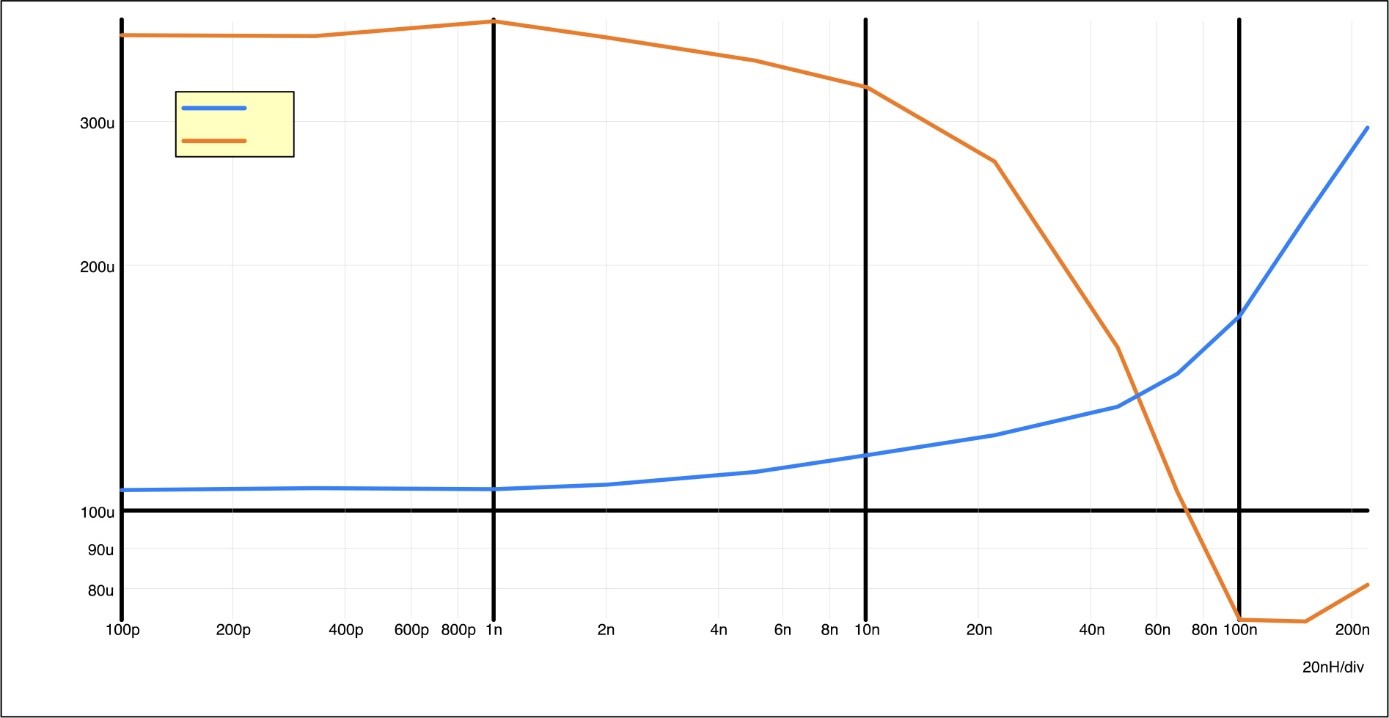

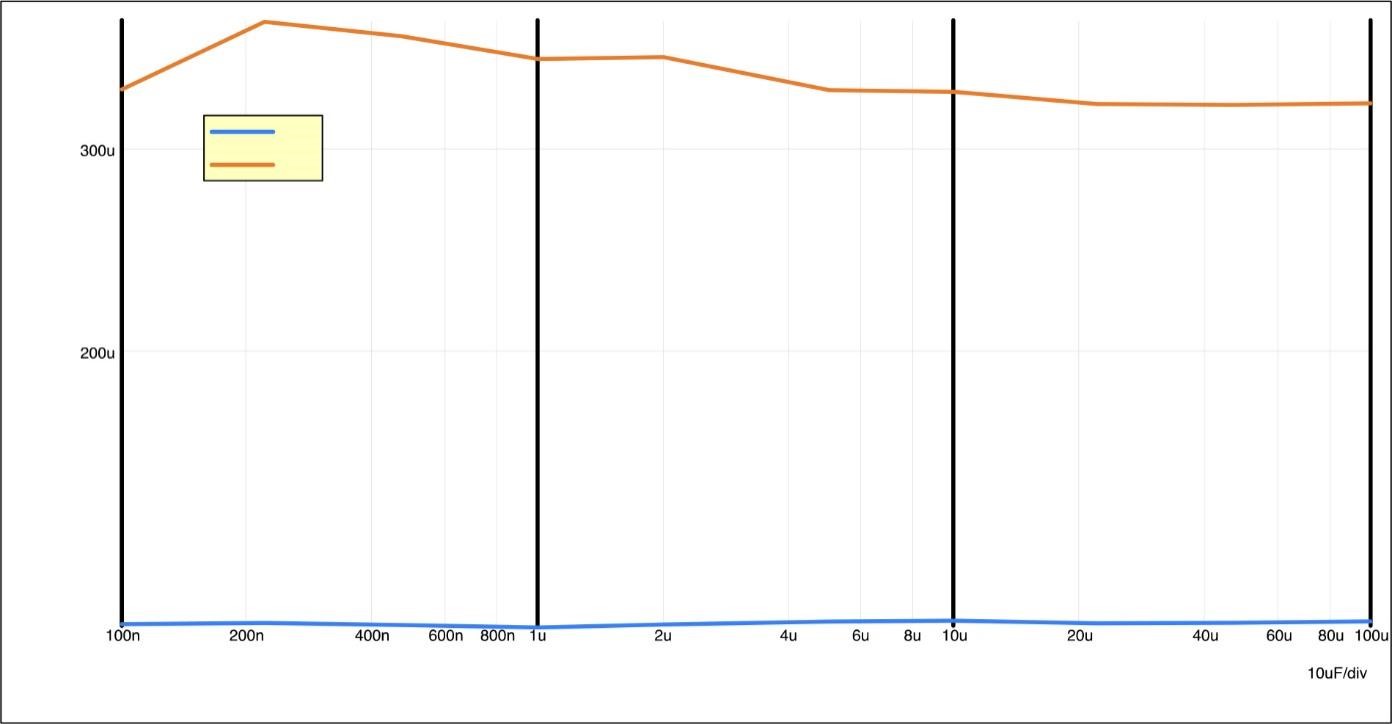

图 14 显示与去耦电容值的函数关系的相同曲线(Eon、Eoff)。

图 14.去耦电容对导通和关断损耗的影响

低于 200 nF,Eon 降低,因为漏电压也急剧降低。在 1 µF 和 10 µF 之间,Eon 略有下降,这微乎其微。高于 10 µF,对 Eon 的影响可以忽略不计。因此,对于 40 A 范围内的电流,1 µF 至 10 µF 之间的去耦电容值较为适合。

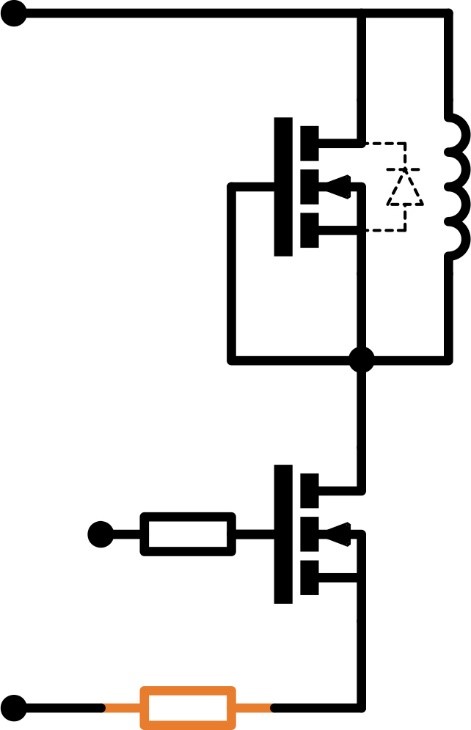

分流电阻

用于感测电流的分流电阻具有电阻损耗,它可以轻微抑制(由于值相对较低)由 PCB 漏感、负载电感电容和去耦电容组成的谐振网络。

在双脉冲测试中接入一个分流电阻可以证明分流(及其位置)是否会影响损耗。(参见图 15)

图 15.用于仿真双脉冲测试仪损耗的分流电阻

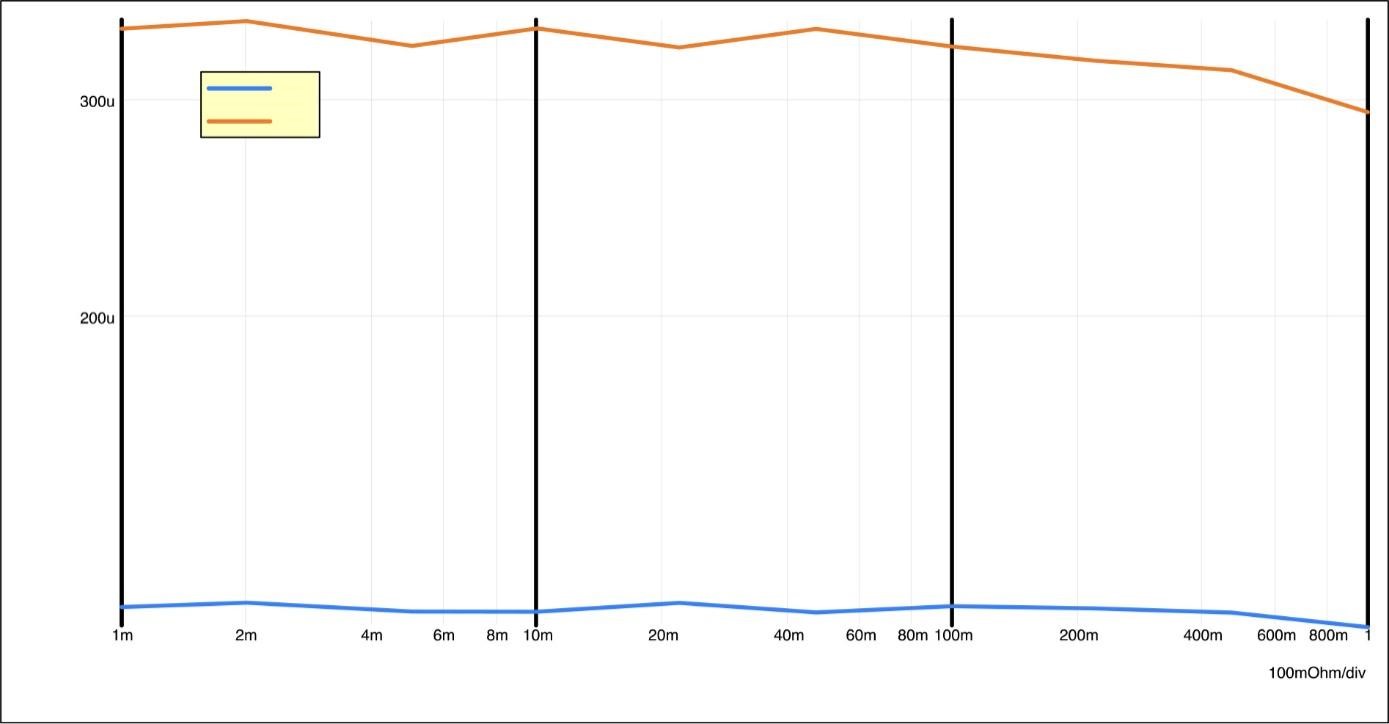

图 16 绘制损耗与分流电阻值的函数关系。

图 16.分流电阻对导通和关断损耗的影响

对于40 A 电流的不切实际的大分流电阻值会降低 Eon 和 Eoff 损耗。然而,当分流电阻的值高于 100 mΩ 时,减少的能量损耗并不能补偿分流电阻上增加的导通损耗。

测量方法。

要生成表示器件损耗的 Eon 和 Eoff,必须构建尽可能理想且寄生效应很小的双脉冲测试仪。在这种情况下,需应用具有极低寄生电容的电感、极短开关环路和高去耦电容值。因为该设置不适用于大规模生产,所以任何选定的元器件的成本或尺寸都无关紧要

根据应用重点使用半桥或四分之一桥结构。对于太阳能升压应用,四分之一桥是首选。对于其他应用,半桥是首选。

双脉冲测试是测量损耗的好方法吗?

如果我们想要在寄生元件影响最小的情况下测量最低损耗,答案是“是的”,具体取决于测试平台的质量。安森美先进的双脉冲测试平台是实现此目的非常好的工具。它可以比较 安森美不同代次下各种芯片尺寸(和 RDS(on))和封装的产品组合和。

然而,紧随其后的问题是什么样的损耗对客户及其应用有影响?安森美测试平台是双脉冲测试环境中无数寄生边界条件其中之一。显然,当客户在实际应用中评估损耗时,器件将不会在 安森美测试环境中运行。例如,数据表中给出的损耗值无法反映客户环境中的损耗。

评估客户应用中损耗的最佳方法是在特定的双脉冲测试仪中引入精确的寄生元件。换句话说,此双脉冲测试变得专用于您的应用。但是,为每个新设计或新客户应用进行新的测量设置或调整现有设置并不切实际。此外,还必须考虑存在多级电路的情况,例如双有源桥。这种情况下,初级和次级在工作点、线路布局和所涉及的元件方面可能不同,例如在特定一侧测量的去耦电容和电感寄生电容。因此,需要调整双脉冲测试平台以评估每一级电路和配置中的损耗。人们很快就意识到,这本身就是一项永无休止的工作。

电力电子设计人员是否有其他方法为其应用获得高度精确的损耗模型?

基于仿真的虚拟平台可替代这种复杂且有限的基于测量的方法。该替代方法只能使用非常精确的器件仿真模型。简而言之仿真优势遵循众所周知的“Garbage-in, Garbage-out”(垃圾进,垃圾出)理论。借助 安森美提供的久经验证的物理和可扩展 SPICE1、2、3、4 模型,设计人员能够通过快速仿真而不是耗时、昂贵的基于测量的方法,为其应用实现最精确的损耗模型。设计人员可以构建参数化仿真,在一个周期内运行多个案例,并通过自动化快速获得结果。安森美深知这种方法给客户带来的巨大益处,推出了 PLECS 模型自助生成工具 (SSPMG),可在 这里 获取。

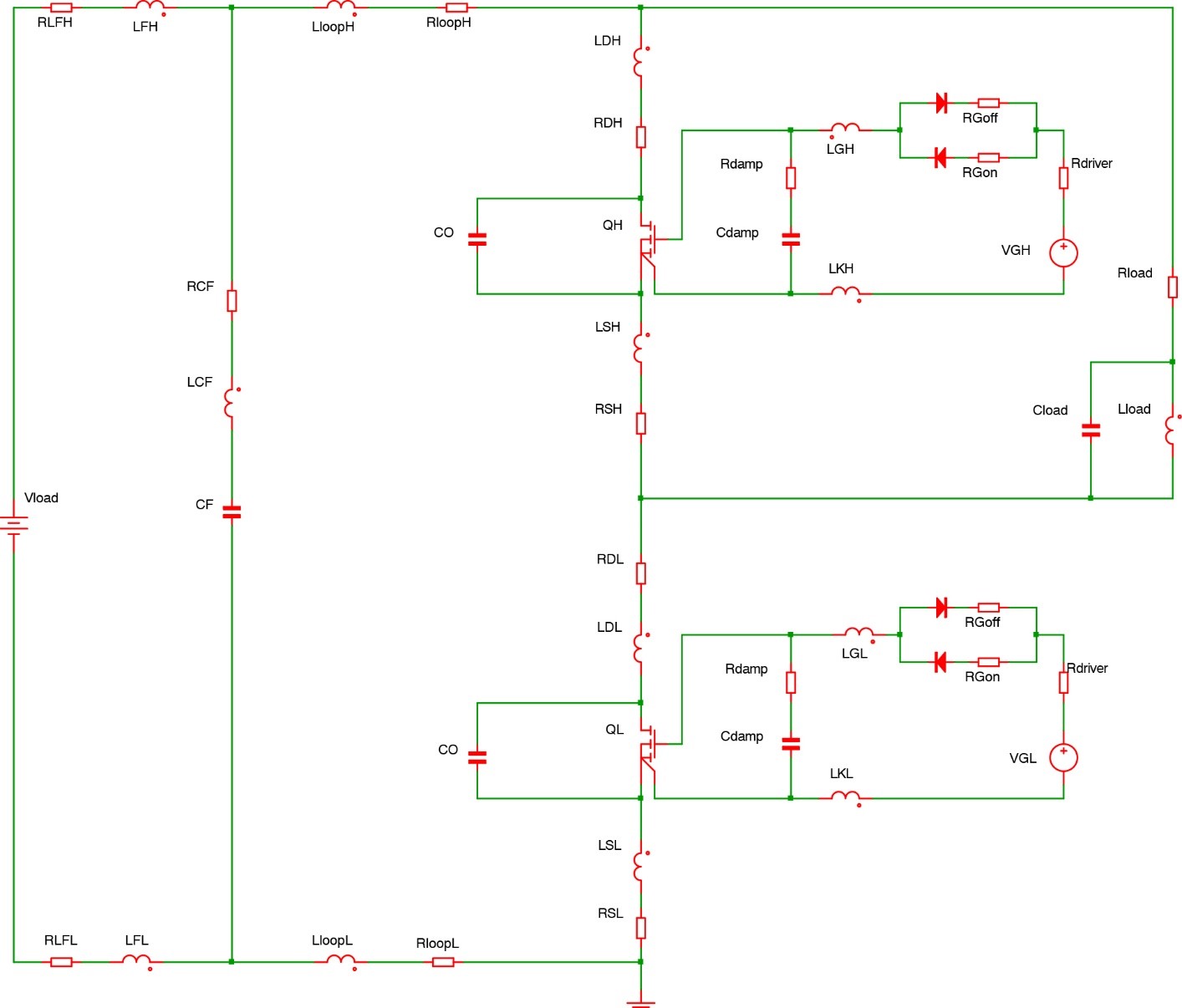

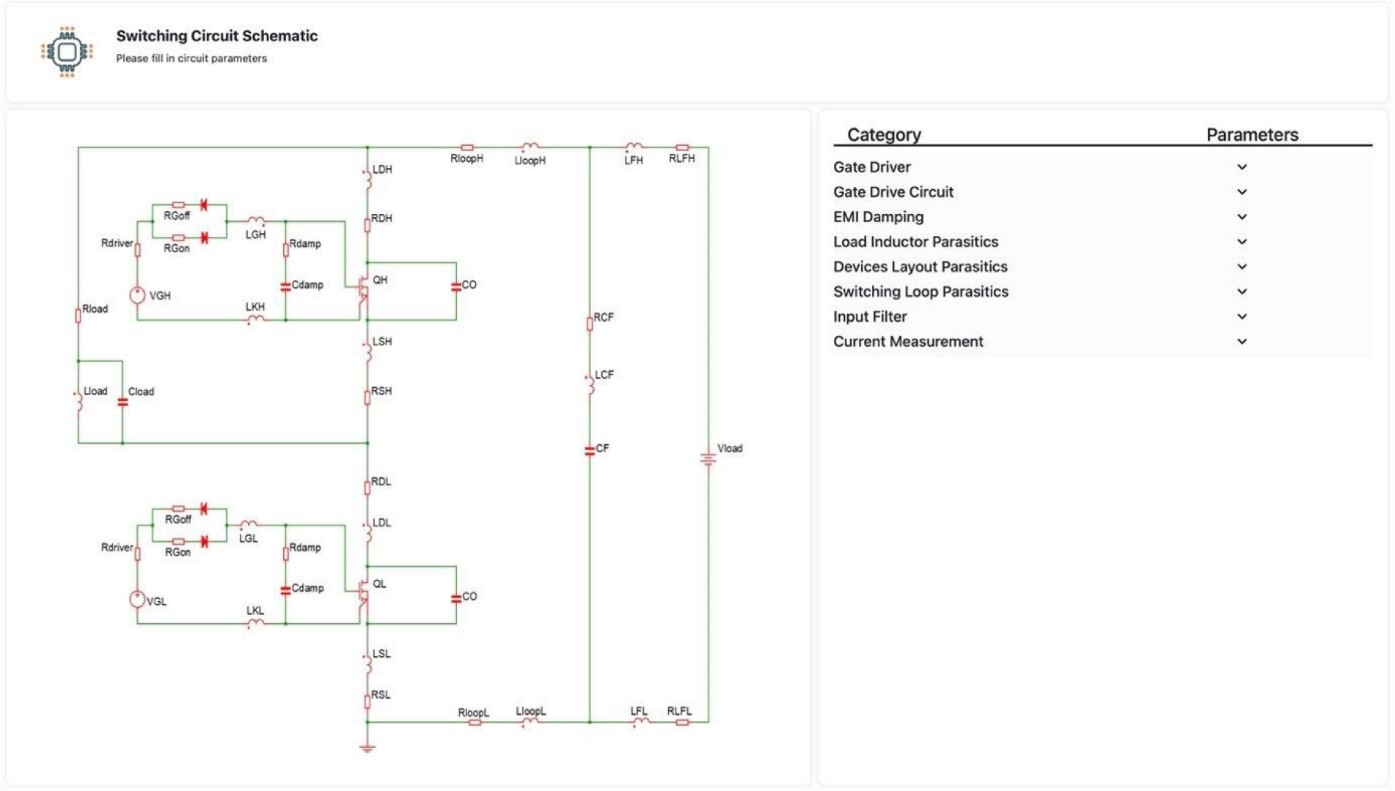

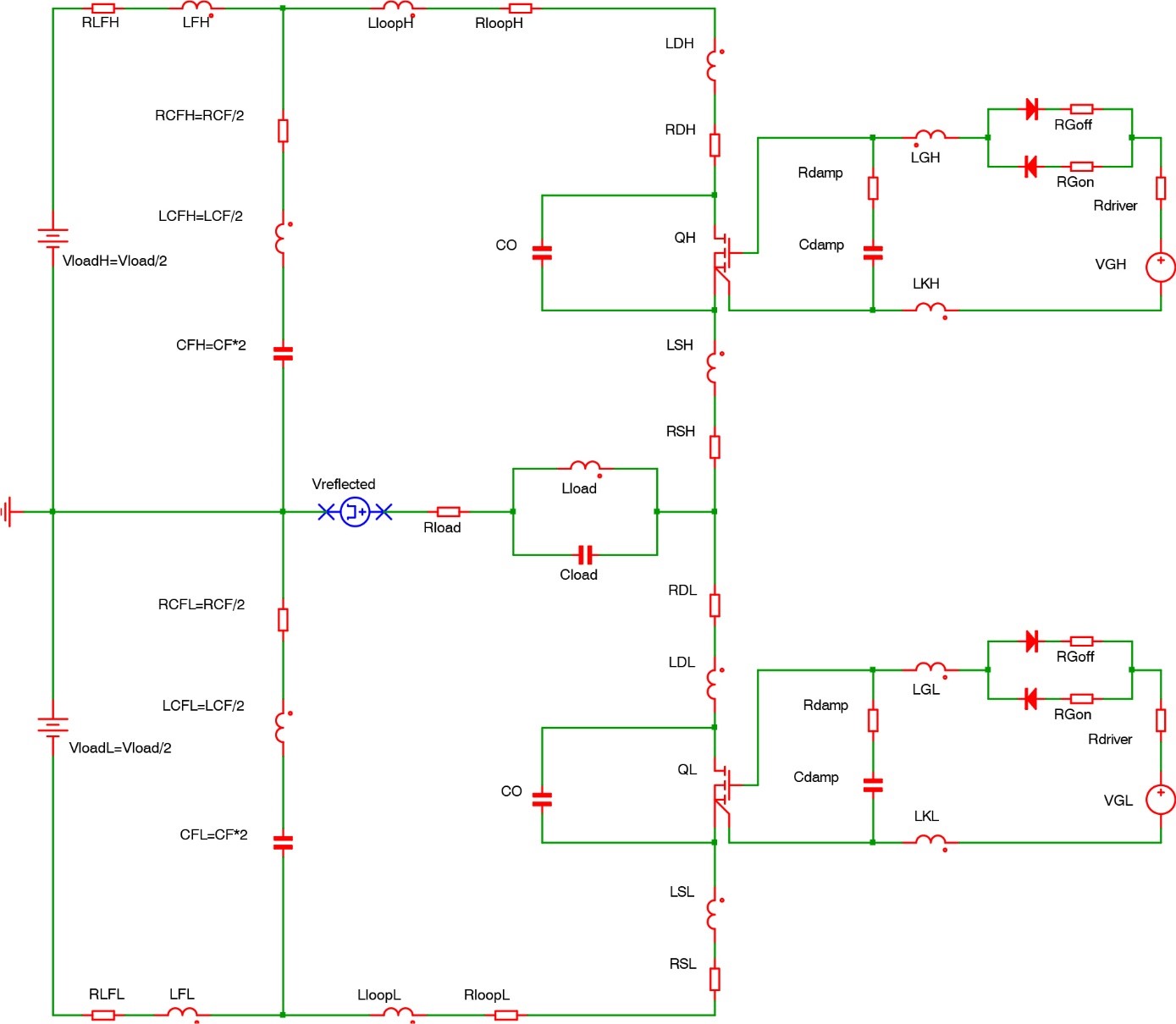

扩展的开关损耗仿真原理图 PLECS 模型

在 SSPMG 中,onsemi 已纳入 30 多个参数来调整双脉冲测试仪仿真原理图,以提取 SiC MOSFET 分立器件和功率模块损耗。图 18 显示分立式产品的原理图。所有参数都是为了反映应用中的所有特定情况和所有可能的电路级数。此外,还可以定制栅极驱动电压。

图 17.引入寄生效应以反映实际应用的分立式产品典型双脉冲测试仪原理图

图 18.用于 PLECS 生成模型的分立式产品双脉冲测试仪原理图

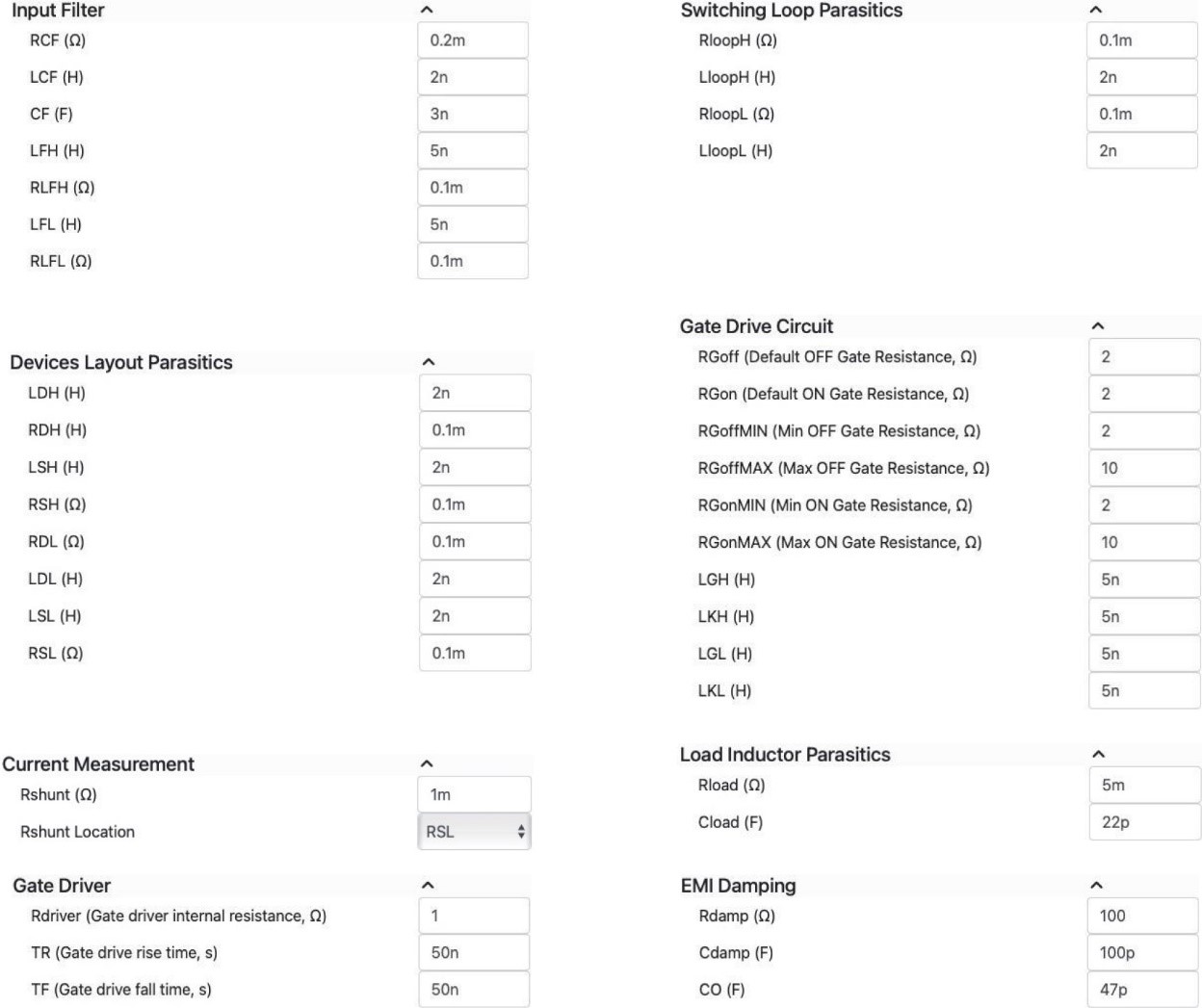

为了生成 PLECS 模型,用户在图 18 右侧所示的表格中输入原理图的参数值。完整列表如图 19 所示。

图 19.双脉冲测试仪生成 PLECS 模型的示例参数值

用户根据工程专业知识、布局限制、寄生参数合理值、电路结构输入参数,

并非需要所有参数,有些可能不会出现在用户应用案例中。例如,出于 EMI 目的,可能使用也可能不使用并联在漏极-源极之间的电容来抑制漏电压 dv/dt。

默认情况下,大多数参数设置为零。在这种情况下,它仅反映器件性能,不反映特定使用情况下的器件性能。

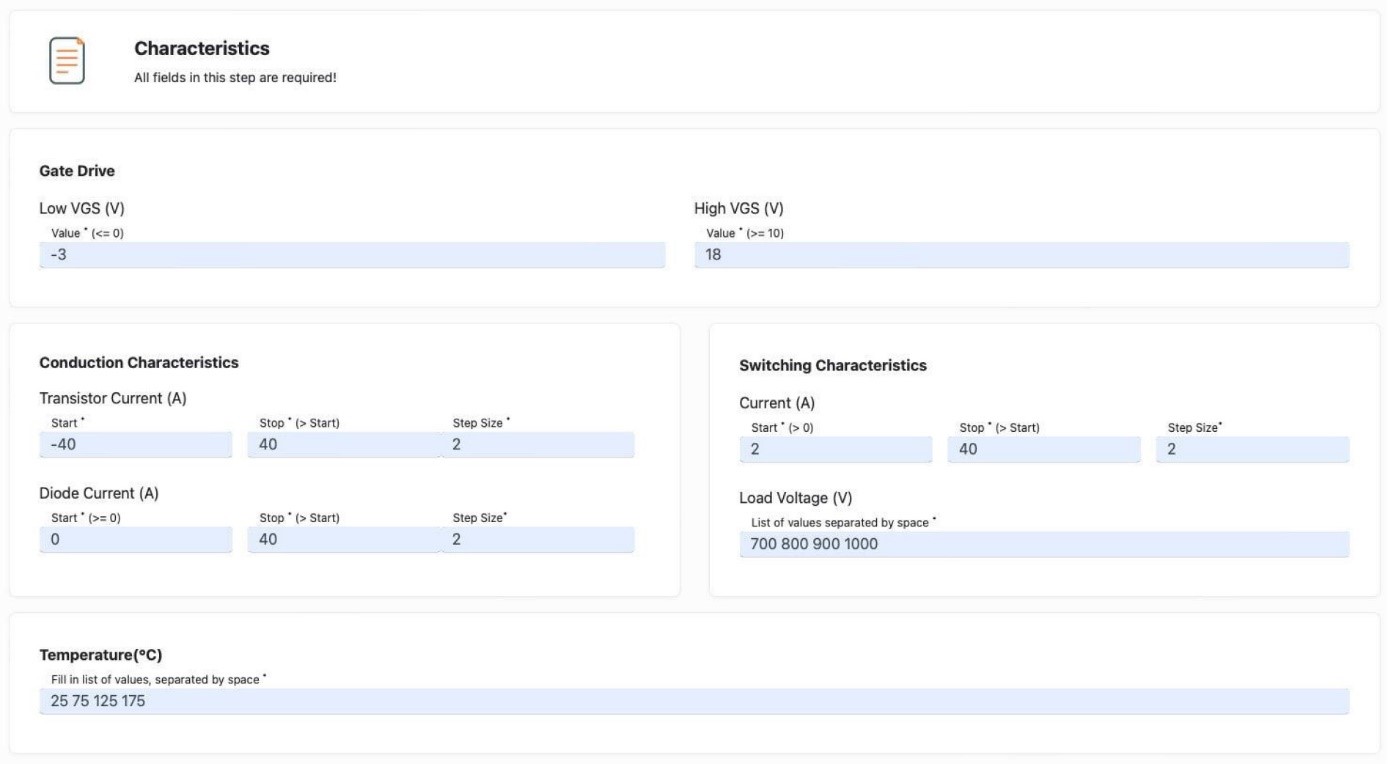

图 20 显示用于生成硬开关 PLECS 模型的 SSPMG 工作范围定义。

图 20.仅硬开关的工作范围设置

通过 PLECS 模型中的密集损耗表提高精度。

如前所述,半导体的导通损耗和开关损耗都与电流、电压和温度呈高度非线性关系。由于测量非常耗时,典型的基于数据表的 PLECS 模型不是很密集。这会直接导致电路仿真时插值不够精确,推导也相当不精确,如图21 所示。在 SSPMG 中,用户可以根据自己的需要设置损耗表的范围(在器件规格限制内)和密度。几分钟内即可获得结果。借助此功能,用户可以在电路仿真过程中确保 PLECS 的精确插值和不用推导。Elite Power 仿真工具中的默认 PLECS 模型本质上已经很密集。

图 21.利用小数据集和大数据集插值和外推错误

利用密集的数据集,PLECS 进行的用于评估开关和导通损耗的插值将更加精确。这反过来又确保了对损耗、效率和温度的精确应用分析。

在 PLECS 模型中包含软开关

传统双脉冲测试中未获得的一项缺失和关键信息是软开关操作情况下的损耗。典型双脉冲测试仪只适用于硬开关。

熟悉软开关技术(LLC、CLLC 等全谐振级或者全桥相移或双有源桥等暂态谐振级)的设计人员都知道,如果在发生开关事件之前有足够的谐振能量,就可以实现软开关。否则,如果能量低于所需量,则可以实现部分软开关,在谐振回路完全没有谐振能量的情况下,甚至就是硬开关。

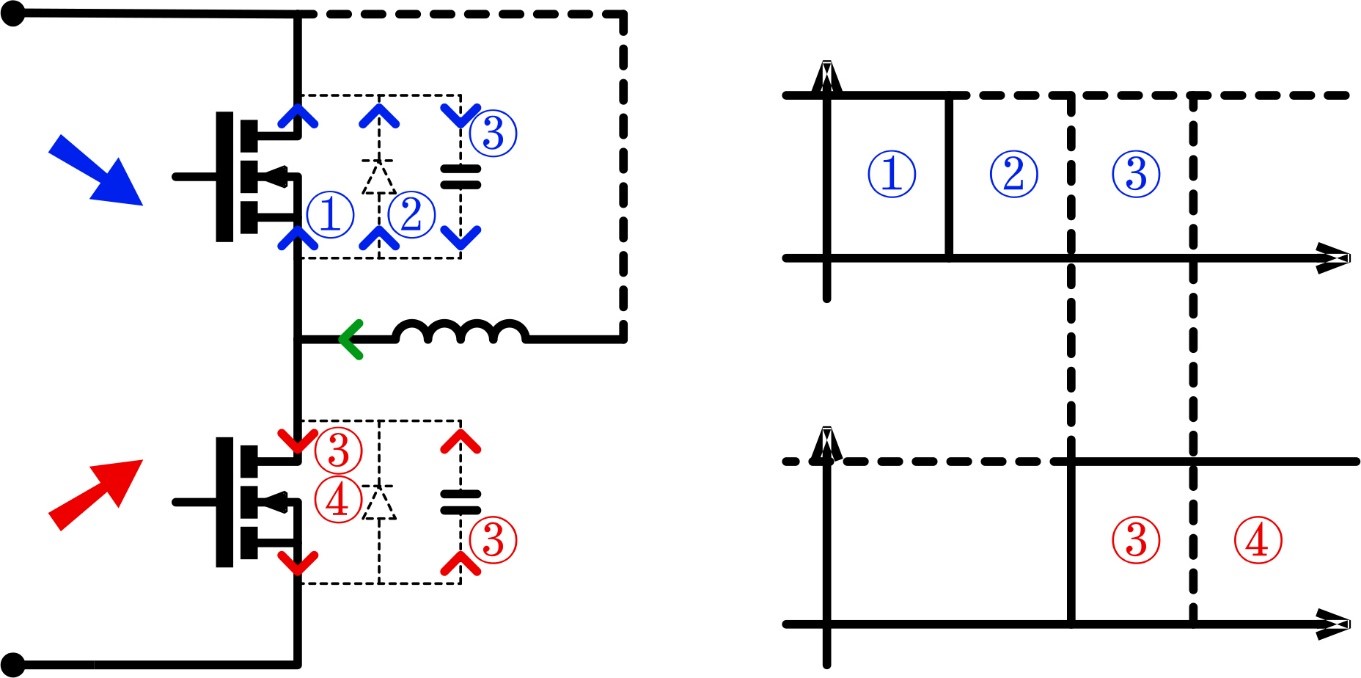

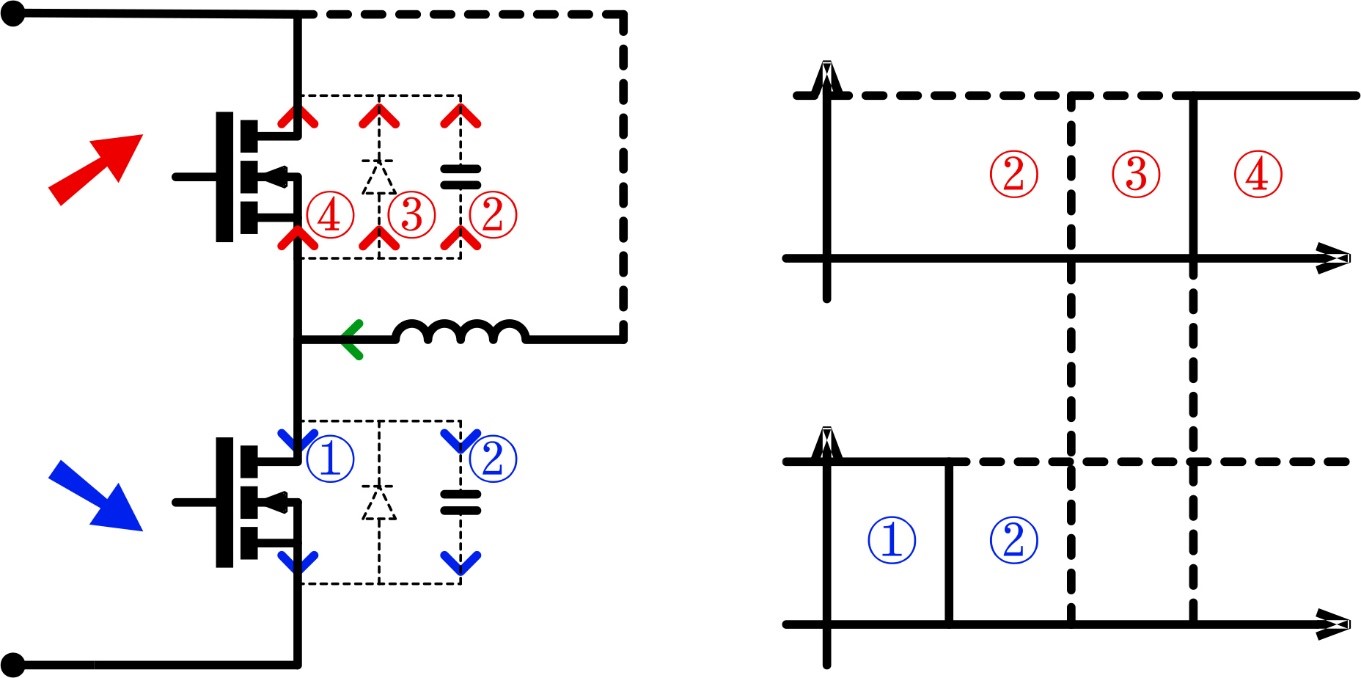

以下基本原理图显示了硬开关和软开关转换电流(参见图 22 和 23)。

图 22.硬开关转换

在硬开关转换中,存储在导通器件中的能量在导通的器件中丢失。在软开关中,此能量从导通的器件转移到关断的器件,对比图 23 和图 22 可以看出。

图 23.软开关转换

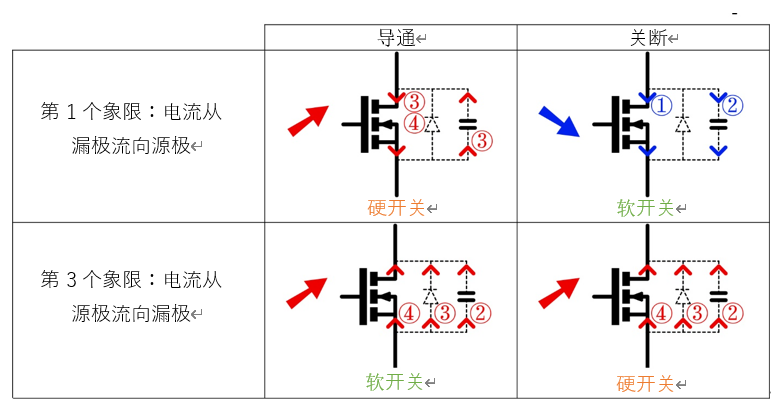

开关事件在图24 下恢复。对于关断事件,所示的开关电流方向是开关事件或关断之前的方向。对于导通事件,所示的开关电流方向是开关事件或导通之后的方向。

图 24.开关事件合成

安森美新的Elite Power 仿真工具和 SSPMG 中包含了适用于软开关的PLECS 模型,该工具在典型双脉冲测试仪中引入了一个小的修改(参见图 17),以便以软开关方式工作(参见图25)。它还包含其他参数,以在发生开关事件时捕捉谐振电感中的 dI/dt。

图 25.引入寄生效应以反映实际应用的分立式产品软开关双脉冲测试仪原理图

![]()

![]()

根据法拉第感应定律 E=L*dI/dt,此 dI/dt 直接与谐振电感电压关联。“反射”电压源代表变压器电压,有助于设置谐振电感中的 dI/dt。

用户还可以输入发生谐振转换时高边侧和低边侧开关之间允许的最大死区时间。用户可以在 SSPMG 中选择硬或软开关类型。当用户输入选择软开关操作时,所有附加的软开关相关参数会自动出现,如图 26 所示。

图 26.硬开关和软开关的工作范围设置

有了这些额外的参数,安森美让客户能够预测硬开关、软开关或部分软开关的任何开关情况下的损耗。

设计人员现在可以了解其应用针对特定设计或参数集的真实性能或损耗。他们还可以看到模式之间的转换发生在哪些工作点,以及对损耗、效率或温度的影响。

安森美通过用于损耗生成模型的 SSPMG 和用于应用仿真的 Elite Power 仿真工具,以非常易于使用和简单的方式简化了软开关拓扑性能的评估。

边界 PLECS 模型生成

传统的基于测量的 PLECS 模型适用于制造中的典型或标称过程案例。安森美已根据实际制造分布为 SiC MOSFET 开发了精确的边界和统计学 SPICE 模型。利用这些器件级边界模型,安森美让 SSPMG 和 Elite Power 仿真工具的用户能够在系统级探索其应用对半导体工艺变化的稳健性。栅极氧化层厚度、电子迁移率和外延区掺杂浓度(仅举几例)等不相关的工艺参数共同作用,导致阈值电压 Vth、RDS(on) 和电容等电气参数产生相关变化。电气参数的变化反过来会引起 PLECS 模型中包含的导通和开关能量损耗的变化。表 1 捕捉 SiC MOSFET 电气参数和 PLECS 模型基于物理的相关性。例如,物理意义上最坏情况下的导通损耗和最坏情况下的开关损耗不会同时发生。

表 1.PLECS 边界模型

电气参数 | PLECS 模型 | ||||

边界工况 | Vth | RDSon | 电容 | 导通损耗 | 开关能量损耗 |

标称值 | 标称值 | 标称值 | 标称值 | 标称值 | 标称值 |

1 | 高 | 高 | 低 | 最差 | 最好 |

2 | 低 | 低 | 高 | 最好 | 最差 |

根据应用,导通和开关能量损耗对整体系统性能的影响会有所不同。安森美边界 PLECS 模型让用户可以灵活地研究整个相关空间。

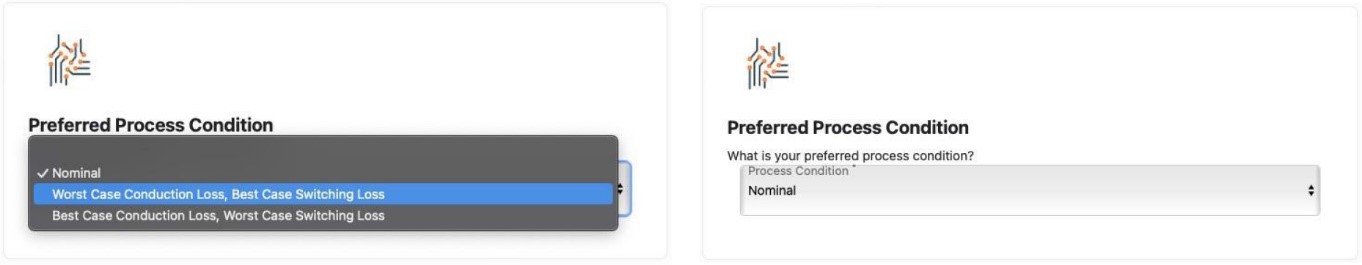

在 SSPMG 中生成自定义 PLECS 模型时,用户可以轻松选择边界工况,如图 27 中所示的边界工况选择。

图 27.在 SSPMG 中选择工艺角条件

在 Elite Power 仿真工具中,用户可以在“器件配置”步骤中为默认的 PLECS 模型选择边界工况。

总结

安森美推进 PLECS 模型生成和仿真的技术水平发展,助力客户在系统级仿真中取得成功。凭借突破性的 SSPMG 平台,客户应用寄生元件、密集的工作条件和半导体工艺变化的影响可被整合进PLECS 模型。单纯依靠测量技术是无法实现所有这些功能的。此外,安森美的这套工具让客户首次得以生成适用于软开关的准确 PLECS 模型。在许多情况下,应用设计人员可以避免由于估算错误以及设计周期长于预期而导致的大量重复设计。

由于嵌入式 PLECS 模型具有高保真度,新型 Elite Power 仿真工具提供了一种可以快速、精确地估算损耗的工具。用户可以将基于 SSPMG 的模型直接上传到 Elite Power 仿真工具,全部在线完成。也就是说,Elite Power 仿真工具的用户能够结合 PLECS 的快速在线功能来预测设计性能(损耗、温度、ZVT/ZVS、效率)。对于新设计,他们不仅可以快速分析多个 Elite SiC MOSFET 或模块之间的折中方案,还可以评估设计或原理图中与开关交互的其他寄生元件的权衡取舍。

参考文献

[1]An Introduction to Physical Scalable Models for Wide Bandgap Power Semiconductor − Part One (Blog article)

https://www.onsemi.com/blog/industrial−cloud−po wer/wide−band−gap−ecosystem−part−i

[2]Wide Bandgap Power Semiconductor: Silicon Carbide MOSFET Models − Part Two − (Blog Article) https://www.onsemi.com/blog/industrial−cloud−po wer/wide−band−gap−ecosystem−switches−disrupti ve−environments

[3]Wide Bandgap Semiconductor Simulation Model Verification − Part Three − (Blog Article) https://www.onsemi.com/blog/industrial−cloud−po wer/wide−bandgap−semiconductor−simulation−m odel−verification

[4]Physically Based, Scalable SPICE Modeling Methodologies for Modern Power Electronic Devices (White paper) −https://www.onsemi.com/pub/Collateral/TND6260−D.PDF

[5]PLECS website : https://www.plexim.com/products/plecs

[6]SiC Simulation − (White paper) https://www.onsemi.com/pub/collateral/tnd6395−d.pdf

[7]Using Physical and Scalable Simulation Models to Evaluate Parameters and Application Results (White paper) − https://www.onsemi.com/pub/collateral/ tnd6330−d.pdf

[8]SiC MOSFET Corner and Statistical SPICE Model Generation − Proceeding of International Symposium on Power Semiconductor Devices and ICs (ISPSD)2020, pp. 154−147, September 2202 https://ieeexplore.ieee.org/document/9170091