作者:电子创新网张国斌

今天 ,一年一度的台积电技术研讨会如期举行,台积电一众高管纷纷亮相,分享了台积电最新的技术路线以及对产业未来趋势的看法,笔者根据会议分享的资料整理了本次研讨会一些重要发布信息!

台积电认为随着 AI、5G 和其他先进工艺技术的发展,全球正通过智能边缘网络产生大量的运算工作负载,因此需要更快、更节能的芯片来满足此需求。

预计到2030年,因需求激增,全球半导体市场将达到约 1万亿 美元规模,其中高性能计算(HPC)相关应用占 40%、智能手机占 30%、汽车占 15%、物联网占10%。

2022年,台积公司与其合作伙伴共创造了超过 12,000 种创新产品,运用近 300 种不同的台积公司技术。台积电持续投资先进逻辑工艺、3DFabric 和特殊制程等技术,在适当的时间提供合适的技术,协助推动客户创新。

一些重要信息:

1、 随着台积电的先进工艺技术从 10 纳米发展至 2 纳米,台积电的能源效率在约十年间以 15% 的年复合增长率提升,以支持半导体产业的惊人成长。

2、台积电先进工艺技术的产能年复合增长率在 2019 年至 2023 年间将超过40%。

3、 作为第一家于 2020 年开始量产 5 纳米的晶圆厂,台积电通过推出 N4、N4P、N4X 和 N5A 等技术,持续强化其 5 纳米工艺家族。

4、 台积电的 3 纳米工艺技术是半导体产业中第一个实现高量产和高良率的工艺技术,台积电预计 3 纳米将在移动和 HPC 应用的驱动下快速、顺利地实现产能提升(ramping)。台积电还推出 N3P 和 N3X 来提升工艺技术价值,在提供额外性能和面积优势的同时,还保持了与 N3E 的设计规则兼容性,能够最大程度地实现 IP 复用。此外,台积电还推出了业界第一个基于3纳米的Auto Early技术,命名为N3AE。N3AE提供以N3E为基础的汽车制程设计套件(PDK),让客户能够提早采用3纳米技术来设计汽车应用产品,以便于2025年及时采用届时已全面通过汽车制程验证的N3A 工艺技术。

5、为了进一步发展微缩技术,以在单芯片片上系统(monolithic SoCs)中实现更小且更优异的晶体管,台积电还在开发 3DFabric 技术,发挥异质整合的优势,将系统中的晶体管数量提高5倍,甚至更多。

6、 从2017年到2022年,台积电对特殊工艺技术投资的年复合增长率超过40%。到2026年,台积公司预计将特殊工艺产能提升近50%。

台积电主要领先工艺技术介绍

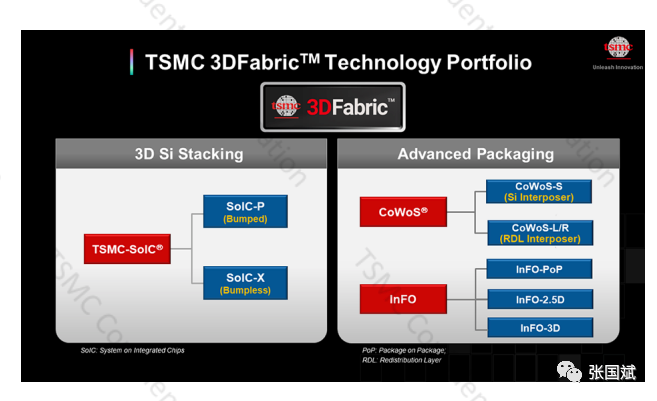

1、TSMC 3DFabric技术

台积电3DFabric 系统整合技术包括各种先进的 3D 芯片堆叠和先进封装技术,以支持广泛的下一代产品:在 3D 芯片堆叠方面,台积电在系统整合芯片(TSMC-SoIC®)技术家族中加入微凸块的 SoIC-P,以支持更具成本敏感度的应用。

2、2.5D CoWoS 平台得以实现先进逻辑和高频宽记忆体的整合,适用于人工智能、机器学习和数据中心等 HPC 应用;整合型扇出层叠封装技术(InFOPoP)和 InFO-3D 支持移动应用,InFO-2.5D 则支持 HPC 小芯片整合。

3、基于堆叠芯片技术的系统整合芯片(SoIC)现可被整合于整合型扇出(InFO)或 CoWoS 封装中,以实现最终系统整合。

CoWoS® 家族

o 主要针对需要整合先进逻辑和高带宽存储器的 HPC 应用。台积公司已经支持超过 25 个客户的 140 多种 CoWoS 产品。

o 所有 CoWoS 解决方案的中介层面积均在增加,以便整合更多先进芯片和高带宽存储器的堆叠,以满足更高的性能需求。

o 台积电正在开发具有高达 6 个光罩尺寸(约 5,000 平方毫米)重布线层(RDL)中介层的 CoWoS 解决方案,能够容纳 12 个高带宽存储器堆叠。

InFO 工艺技术

o 在移动应用方面,InFO PoP 自 2016 年开始量产并运用于高端移动设备,可以在更小的封装规格中容纳更大、更厚的系统级芯片(SoC)。

o 在 HPC 应用方面,无基板的 InFO_M 支持高达 500 平方毫米的小芯片整合,适用于对外型尺寸敏感度较高的应用。

3D 芯片堆叠技术

o SoIC-P 采用 18-25 微米间距微凸块堆叠技术,主要针对如移动、物联网等成本较为敏感的应用。

o SoIC-X 采用无凸块堆叠技术,主要针对 HPC 应用。其芯片对晶圆堆叠方案具有 4.5 至 9 微米的键合间距,已在台积公司的 N7 工艺技术中量产,用于HPC 应用。

o SoIC 堆叠芯片可以进一步整合到 CoWoS、InFo 或传统倒装芯片封装,运用于客户的最终产品。

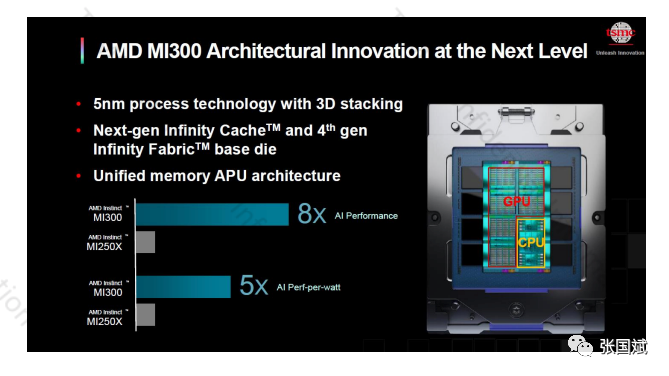

6月14日, AMD 成功展示了采用 SoIC-X 技术将 N5 GPU 和 CPU 堆叠于底层芯片,并整合在CoWoS 封装中,以满足下一代百万兆级(exa-scale)运算的需求,这也是台积电3DFabric 技术推动 HPC 创新的绝佳案例。关于该产品详细介绍可以参看《硬刚英特尔NVIDIA,AMD发布服务器和AI加速器新品,支持800亿参数大模型应用!》

特殊工艺

台积电提供了业界最全面的特殊工艺产品组合,包括电源管理、射频、CMOS 影像感测等,涵盖广泛的应用领域。

汽车

o 随着汽车产业向自动驾驶方向发展,运算需求正在快速增加,且需要最先进的逻辑技术。到 2030 年,台积电预计 90% 的汽车将具备先进驾驶辅助系统(ADAS),其中 L1、L2 和 L2+/L3 将有望分别达到 30% 的市场占有率。

o 在过去三年,台积电推出了汽车设计实现平台(ADEP),通过提供领先业界、Grade 1 品质认证的 N7A 和 N5A 工艺来实现客户在汽车领域的创新。

o 为了让客户在技术成熟前就能预先进行汽车产品设计,台积电推出了 AutoEarly,作为提前启动产品设计并缩短上市时间的垫脚石。

1、N4AE 是基于 N4P 开发的新技术,将允许客户在 2024 年开始进行试产。

2、 N3AE 则成为 N3A 的坚实基础, N3A 将于 2025 年全面通过汽车制程验证,并将成为全球最先进的汽车逻辑工艺技术。

支持 5G 和联网性的先进射频技术

o 台积电在 2021 年推出了 N6RF,该技术是基于公司创纪录的 7 纳米逻辑工艺技术,在速度和能源效率方面均具有同级最佳的晶体管性能。

o 结合了出色的射频性能以及优秀的 7 纳米逻辑速度和能源效率,台积电的客户可以通过从 16FFC 转换到 N6RF,在半数字和半类比的射频 SoC 上实现功耗降低 49%,减免移动设备在能源预算以支持其他不断成长的功能。

o 台积电今日宣布推出最先进的互补式金属氧化物半导体(CMOS)射频技术 N4PRF,预计于 2023 年下半年发布。相较于 N6RF,N4PRF 逻辑密度增加 77%,且在相同效能下,功耗降低45%。N4PRF 也比其前代技术 N6RF 增加了 32%的 MOM 电容密度。

超低功耗

o 台积电的超低功耗解决方案持续推动降低 Vdd,以实现对电子产品而言至关重要的节能。

o 台积电不断提升技术水平,从 55ULP 的最小 Vdd 为 0.9V,到 N6e 的 Vdd已低于 0.4V,我们提供广泛的电压操作范围,以实现动态电压调节设计来达成最佳的功耗∕性能。

o 相较于 N22 解决方案,即将推出的 N6e 解决方案可提供约 4.9 倍的逻辑密度,并可降低超过 70%的功耗,为穿戴式设备提供极具吸引力的解决方案。

MCU / 嵌入式非挥发性存储器

o 台积电最先进的 eNVM 技术已经发展到了基于 16/12 纳米的鳍式场效应晶体管(FinFET)技术,令客户能够从 FinFET 晶体管架构的优秀性能中获益。

o 由于传统的浮闸式 eNVM 或 ESF3 技术越来越复杂台积电还大量投资于RRAM 和 MRAM 等新的嵌入式存储器技术。 这两种新技术都已经取得了成果,正在 22 纳米和 40 纳米上投产。

o 台积电正在计划开发 6 纳米 eNVM 技术

RRAM:已经于 2022 年第一季开始生产 40/28/22 纳米的 RRAM。

o 台积电的 28 纳米 RRAM 进展顺利,具备可靠效能,适于汽车应用。

o 台积电正在开发下一代的 12 纳米 RRAM,预计在 2024 年第一季就绪。

- MRAM:2020 年开始生产的 22 纳米 MRAM 主要用于物联网应用,现在,台积电正在与客户合作将 MRAM 技术用于未来的汽车应用,并预计在 2023 年第二季取得 Grade 1 汽车等级认证。

CMOS 影像感测

o 虽然智能手机的相机模组一直是互补式金属氧化物半导体(CMOS)影像感测技术的主要驱动力,但台积公司预计车用相机将推动下一波 CMOS 影像感测器(CIS)的增长。

o 为了满足未来感测器的需求,实现更高品质且更智能的感测,台积电一直致力于研究多晶圆堆叠解决方案,以展示新的感测器架构,例如堆叠像素感测器、最小体积的全域快门感测器、基于事件的 RGB 融合感测器,以及具有集成存储器的 AI 感测器。

显示器

o 在 5G、人工智能和 AR/VR 等技术驱动下,台积电正致力于为许多新应用提供更高的分辨率和更低的功耗。

o 下一代高阶 OLED 面板将需要更多的数字逻辑和静态随机存取存储器(SRAM)内容,以及更快的帧率,为了满足此类需求,台积公司正在将其高压(HV)技术导入到 28 奈纳米的产品中,以实现更好的能源效率和更高的静态随机存取存储密度。

o 台积电领先的 µDisplay on silicon 技术可以提供高达 10 倍的像素密度,以实现如 AR 和 VR 中使用的近眼显示器所需之更高分辨率。

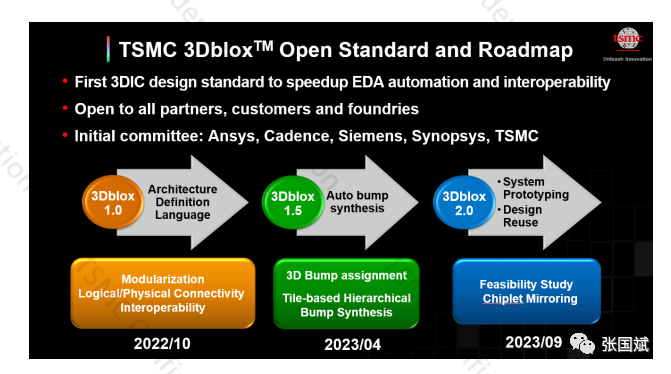

3DFabric™ 联盟和 3Dblox™ 标准

在去年的开放创新平台(Open Innovation Platform® ,OIP)论坛上,台积电宣布推出新的 3DFabric™ 联盟,这是继 IP 联盟、电子设计自动化(EDA)联盟、设计中心联盟(DCA)、云端(Cloud)联盟和价值链联盟(VCA)之后的第六个 OIP联盟,旨在促进下一代 HPC 和移动设计的生态系统合作,具体包括:

o 提供 3Dblox 开放标准

o 实现存储器和台积公司逻辑工艺之间的紧密协作

o 将基板和测试合作伙伴导入生态系统

- 台积电推出了最新版本的开放式标准设计语言 3Dblox™ 1.5,旨在降低 3D IC 设计的门槛。

卓越制造

为了满足客户不断增长的需求,台积公司加快了晶圆厂拓展的脚步。

o 从 2017 年到 2019 年,台积电平均每年进行大约 2 期的晶圆厂建设工程。

o 从 2020 年到 2023 年,台积公司晶圆厂的平均建设进度大幅增加至每年约5 期的工程。

o 在过去两年,台积公司总共展开了 10 期的晶圆厂新建工程,包括在台湾地区的 5 期晶圆厂工程与 2 期先进封装厂工程,以及全球范围内的 3 期晶圆厂工程。

- 台湾地区以外,28 纳米及以下工艺产能在 2024 年将比 2020 年增加 3 倍。在台湾地区,台积电 N3 制程量产的基地在南科 18 厂;此外,台积电正在为N2 制程的新晶圆厂进行准备。

- 在中国大陆,南京厂新 1 期的 28 纳米制程晶圆厂已于 2022 年开始量产。

- 在美国,台积电正在亚利桑那州建造 2 期晶圆厂。第一期已经开始移入设备,第二期正在兴建中。

- 在日本,台积电正在熊本兴建一座晶圆厂,以提供16 纳米和 28 纳米技术。

- 台积电在先进制程的缺陷密度(D0)和每百万件产品缺陷数(DPPM)方面的领先地位,展现了其制造卓越性。

o N5 工艺复杂度远高于 N7,但在相同阶段,N5 的良率优化比 N7 更好。

o 台积电 N3 工艺技术在高度量产中的良率表现领先业界,其 D0 效能已经与 N5 同期的表现相当。

o 台积电 N7 和 N5 制程技术在包括智能手机、电脑和汽车等方面,展现了领先业界的 DPPM,我们相信 N3 的 DPPM 很快就能追上 N5 的表现。

3DFabric™ 制造技术

o 通过利用台积电领先业界的 3DFabric™ 制造技术,客户可以克服系统级设计复杂性的挑战,加速产品创新。

o CoWoS 和 InFO 家族在量产后很快就达到了相当高的良率。

o SoIC 和先进封装的整合良率将达到与 CoWoS 和 InFO 家族相同的水平。

绿色制造

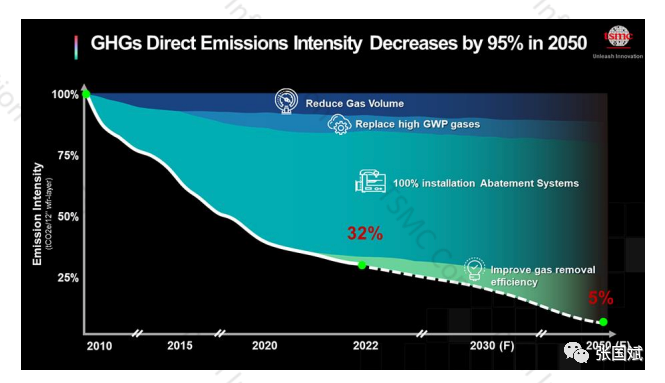

- 为了实现 2050 年净零排放的目标,台积电持续评估并投资各种减少温室气体排放的机会。

o 到 2022 年,台积电直接温室气体排放量已经较 2010 年降低了 32%。

o 此一成果是通过降低工艺气体消耗、替换可能造成全球暖化的气体、安装现场废气处理设备,以及提高气体去除效率等方式实现。

- 台积电目标每个工艺技术于量产第五年时,生产能源效率提高一倍。

o N7 制程技术的生产能源效率在量产后第五年提高了 2.5 倍。

o 台积电预计到 2024 年,N5 制程技术的生产能源效率将提高 2.5 倍。

- 去年,台积电在台湾地区南部建立了第一座再生水厂,每日供水量 5,000 公吨,时至今日,该再生水厂每日供水量达 20,000 公吨。

o 到 2030 年,台积公司的每生产单位自来水消耗量将降至 2020 年的 60%!(完)