作者:电子创新网张国斌

在近两年美国限制中国半导体的发展举措中,EDA工具的限制成为一个有力的手段,这也让很多人知道EDA工具卡住我们IC设计的脖子,但是大家不知道的是半导体IP也被卡脖子,尤其是先进工艺接口IP。不过,随着本土IP公司的茁壮成长,这个问题已经有望解决。

“今年芯耀辉的员工很忙,一部分人在加班加点开发产品,一部分在支持客户规模量产。”在今年的ICCAD2023的媒体专访中,芯耀辉董事长曾克强表示,“经过三年多的自主研发,芯耀辉已开发出基于国产工艺全系列接口IP,包括PCIe、Serdes、DDR、D2D、USB、MIPI、HDMI、SATA,SD/eMMC等涵盖最先进协议标准的全栈式完整IP解决方案,包括LPDDR5、DDR5和片间互联的D2D IP。目前,我们正积极将这些产品引用到行业主流工艺中进行测试,此外,要实现Chiplet技术的真正落地,高质量的接口IP是不可或缺的。”

团队研发的DDR5/4 PHY在相关工艺上超越了全行业最高速率;推出的LPDDR5/4 PHY极具PPA竞争力及优异的易实现性及互操作性;完整的UCIe D2D解决方案包括PHY及控制器,可支持UCIe协议且兼容D2D和C2C场景。

“在芯耀辉之前,大家可以看到国内的厂商基本上能够实现的做到的接口IP的标准一般都还是比较传统的,像DRR3、PCIE3等,但是最领先的标准比如说DDI5、PCIE5没有,这也是我们芯耀辉从成立之日起的时候要做的事情,我们就希望在这一块真正能够做前人没做过的事,真正填补空白。”他强调。“接口IP也是当下整个IP领域需求最旺,增速最快的应用领域,也是除了处理器以外规模最大的细分市场。”

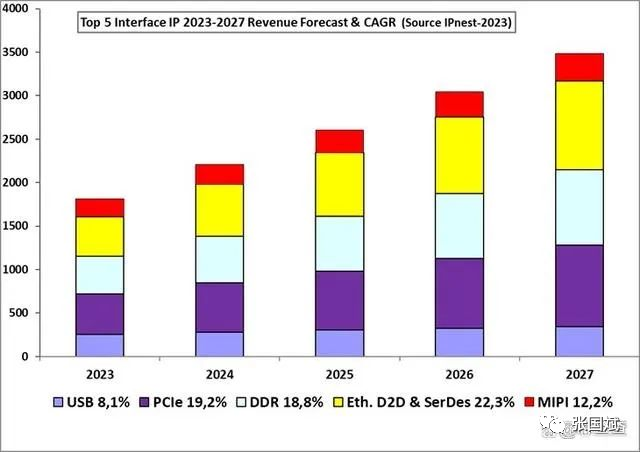

IPnest对接口IP未来5年进行了预测(2023-2027)大部分增长预计来自三个类别:PCIe、内存控制器(DDR)、以太网&D2D,5年复合年增长率分别为19.2%、18.8%和22.3%,这些协议都与数据应用相关。2022年前5大接口协议的市场规模为14.4亿美元,预测2027年将提升至35亿美元,即复合年增长率18%。

曾克强表示,芯耀辉在IP领域拥有独特的优势,主要体现在以下两点:

1、符合国际标准协议的定制化设计:芯耀辉专注于制定符合国际标准协议的接口IP,不仅满足这些标准协议的要求,还根据客户的客户的不同应用场景和产品形态,提供满足这些标准协议的定制化需求。例如,对于消费类产品,客户可能更关注功耗和面积,即所谓的的PPA(功耗、性能、面积),而除了在PPA方面取得平衡外,客户最看重的是一次量产成功,要求IP做到高可靠性和强兼容性。“这也是我们最看重的地方,甚至超过了PPA的考量”他强调。

2、专业团队进行系统级验证:由于芯耀辉在IP领域有持续15-20年的积累,公司建立了几十人的经验丰富专业团队,专门负责可靠性和兼容性测试,从系统级到芯片电路级进行全方位的验证。

“例如,在可靠性方面,芯耀辉会针对IP进行温度、电压以及制造工艺的拉偏测试,并且还会进行ESD静电防护能力测试以及长时间的高温老化测试,确保IP在客户芯片量产上没有良率的问题。同时我们也会针对客户实际应用场景,以及积累多年的非标准场景,进行极端环境下(比如高通道损耗,长时间不间断传输等)的IP性能测试,保障IP具备高度的可靠性。”他补充说,“而在兼容性方面,不同的接口IP都会和市场上主流的相关外设做互联互通兼容测试。举个例子,常用的接口DDR5,针对市场上最常用的应用厂商的颗粒,比如说三星、海力士、美光和国内成熟厂商等等,我们都会收集它主要的颗粒,针对不同的速率、不同的DIMM,我们都会去做测试,不仅是普通的读写,甚至会反复的初始化,考验产品的训练过程和性能,确保接口IP能做到完备的测试,这应该是国内的厂商里独一无二的,所以保证了我们交付给客户的产品,除了在PPA上满足客户的需求,更在可靠性和兼容性上帮助客户的产品一次量产成功,降低产品风险,缩短产品上市时间。”

他表示经过三年的研发,芯耀辉已经在国产先进工艺已经实现了所有接口IP主流的全套量产交付,尤其是针对高性能计算,最主要的应用场景就是CPU、GPU、AI,他们其中主要的接口IP的需求主要是两大类,一类是存储器接口,一类是片间互联。如DDR5、LPDDR5等芯耀辉都已经完成自研,并且实现量产交付。

针对片间互联,芯耀辉的PCIE4、PCIE5都是行业目前独家的,也完成量产交付,包括die to die的UCIe。

“Chiplet技术的核心在于将芯片的性能和工艺进行解耦,将一个复杂的SoC大芯片根据其不同功能分成不同小芯片,这些小芯片可以采用不同的工艺来异构集成。理想情况下,这种集成应该在效率和连接性上类似于同一颗芯片,即像同一颗芯片的片间总线一样高效互联。然而,实际情况下,由于不同芯片的连接会带来一定损耗,而且许多芯片需要大量连线,这带来了一个现实中的问题。要实现Chiplet技术,最本质的挑战是实现片间的高效互联,而真正的互联问题是Chiplet技术落地中最为核心的方面。在这个过程中,对接口IP的需求显得尤为关键”他分析说,“芯耀辉是第一批加入UCIe组织的国内厂商,也是参与制定首个中国原生Chiplet技术标准《小芯片接口总线技术要求》(T/CESA 1248-2023)的重点贡献企业,同时也是中国Chiplet《芯粒互联接口标准(ACC1.0)》和《车规级芯粒互联接口标准(ACC_RV1.0)》的起草和审阅单位;另外,我们还承接了国家科技部重点研发计划“芯粒集成的统一网络架构和接口规范研究”项目,从产学研多方面推动国内Chiplet技术落地及生态链的发展。”

他指出,在开发Chiplet时,封装是一个关键要素。因此,在芯耀辉进行接口IP设计时,他们就考虑了与芯片接口IP设计和封装设计之间的协同设计。芯耀辉已经和国内多家先进封装厂商联合研发,以在提供给客户接口IP时就充分考虑后端封装的实现性。

他表示,芯耀辉不仅支持国外厂商的先进封装,也支持国内一些2.5D封装,同时针对国内产业链的现状,也支持传统标准封装。“芯耀辉是国内第一家完成UCIe die to die的IP。今年年末,我们将完成首个客户量产交付”他强调。

展望未来,他表示芯耀辉看好高性能计算、人工智能和汽车领域。从2021年开始,芯耀辉已经开始在相应的接口IP领域进行布局。截至2023年,芯耀辉已经通过了与车规相应的ACQ-100和ISO26262的国际测试认证。因此,芯耀辉是国内唯一能够提供符合车规认证的接口IP厂商,为未来汽车的市场做好充分的准备。

注:本文为原创文章,未经作者授权严禁转载或部分摘录切割使用,否则我们将保留侵权追诉的权利