作者:电子创新网张国斌

昨天,在发表了《虽然代工业务遭遇挫折,但我希望英特尔能在AI时代迎头赶上,因为...》,英特尔中国联系了我,提供了有关英特尔18A工艺的最新信息。

英特尔强调最新节点上的产品设计和工艺准备进展顺利,已具备更早地过渡到Intel 18A的能力。英特尔即将实现“四年五个制程节点(即在4年内完成Intel 7、Intel 4、Intel 3、Intel 20A和Intel 18A五个先进制程节点)”计划,将提前把工程资源从Intel 20A投入到Intel 18A,按计划于2025年推出Intel 18A。

英特尔强调:

1、Intel 18A在晶圆厂里的生产良好,良率表现优秀,基于Intel 18A的产品已上电运行并顺利启动操作系统。目前,Intel 18A的缺陷密度已经达到D0级别,小于0.40。

2、今年7月,英特尔发布了Intel 18A 制程节点上的设计套件(PDK1.0版本),得到了生态系统的积极响应。

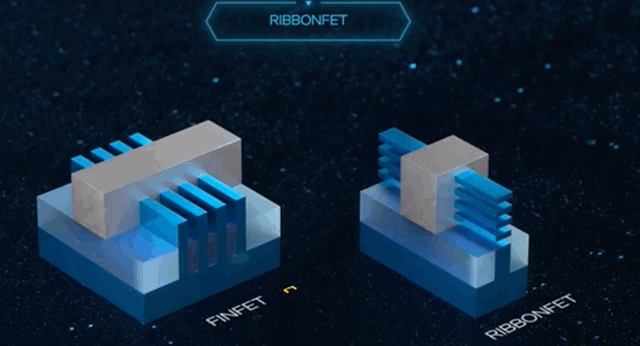

3、通过Intel 20A,英特尔首次成功地集成了RibbonFET全环绕栅极晶体管架构和PowerVia背面供电技术,这两项技术都将用于Intel 18A。这展示了半导体创新的迭代特性,英特尔将把这些进步带给英特尔代工服务的客户。

Intel 18A的开发建立在Intel 20A所奠定的基础之上,体现了英特尔不断探索和完善对推进摩尔定律至关重要的新技术、材料和晶体管架构的实践。

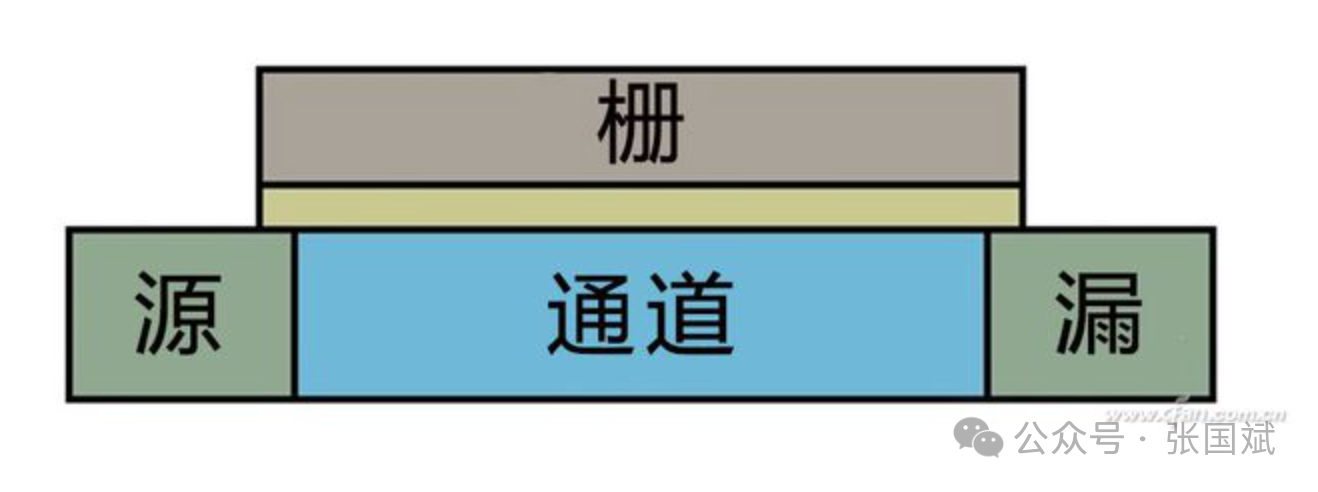

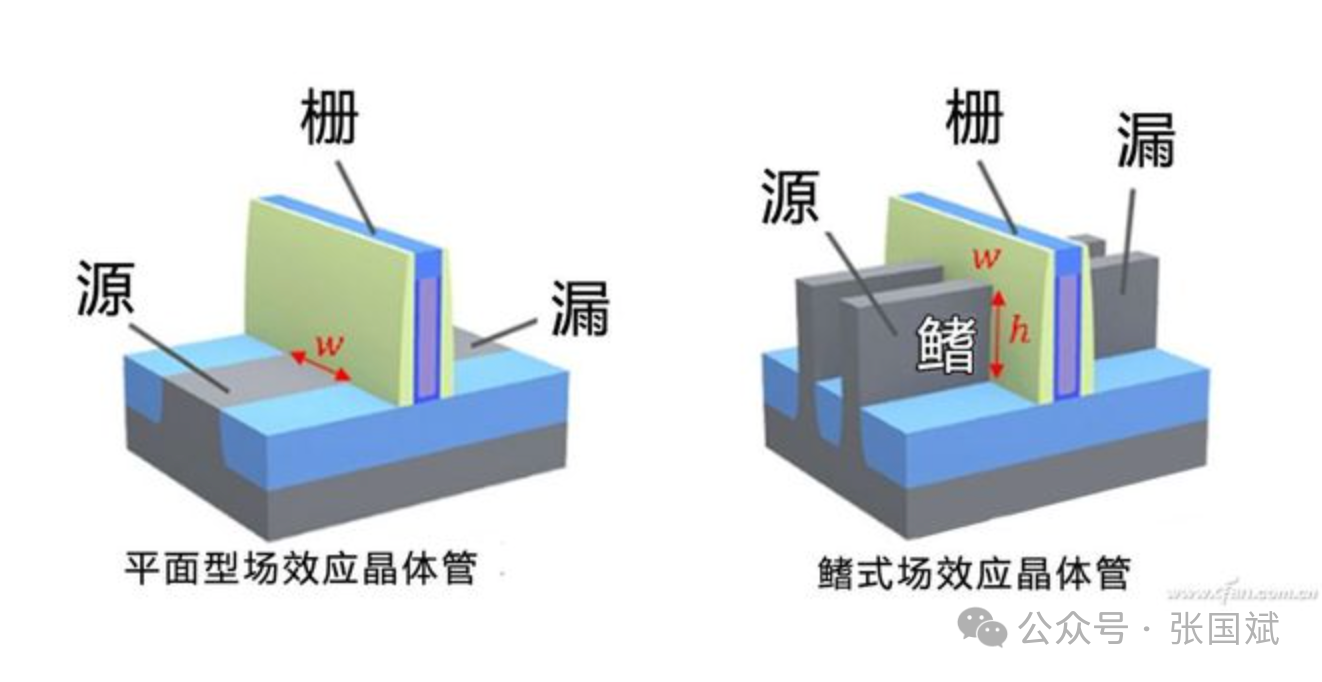

有关Intel 18A工艺,有一个重要的技术术语就是RibbonFET全环绕栅极晶体管架构,其实纵观半导体工艺技术的发展历史,就是一部关于晶体管从平面到立体的发展史。

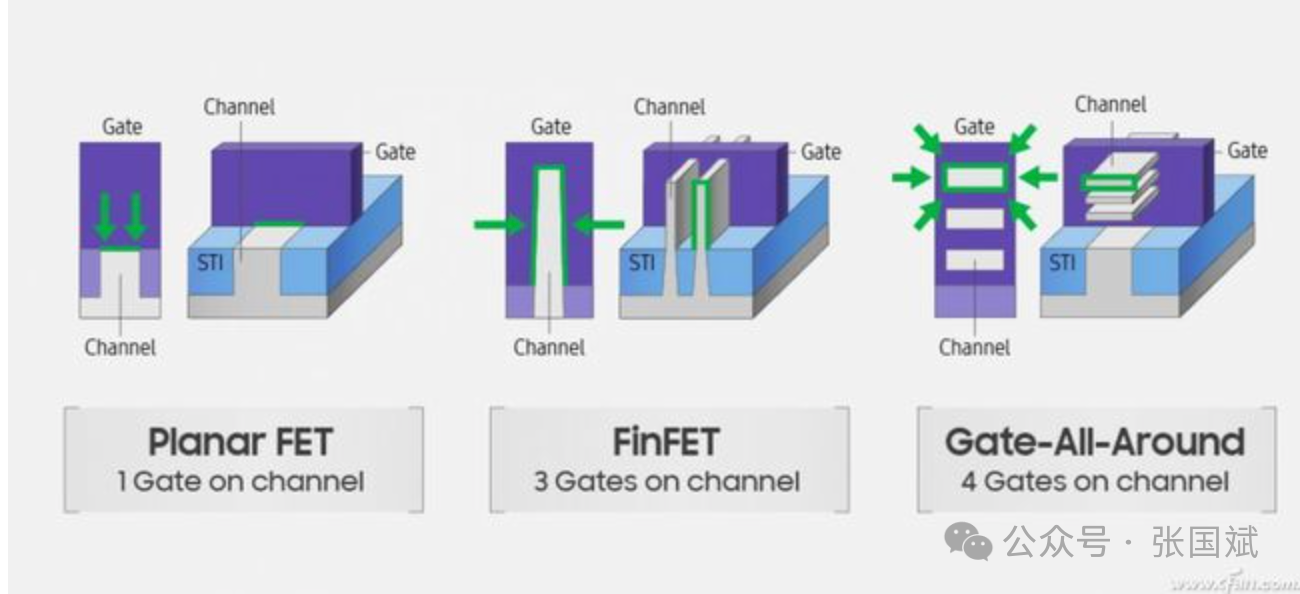

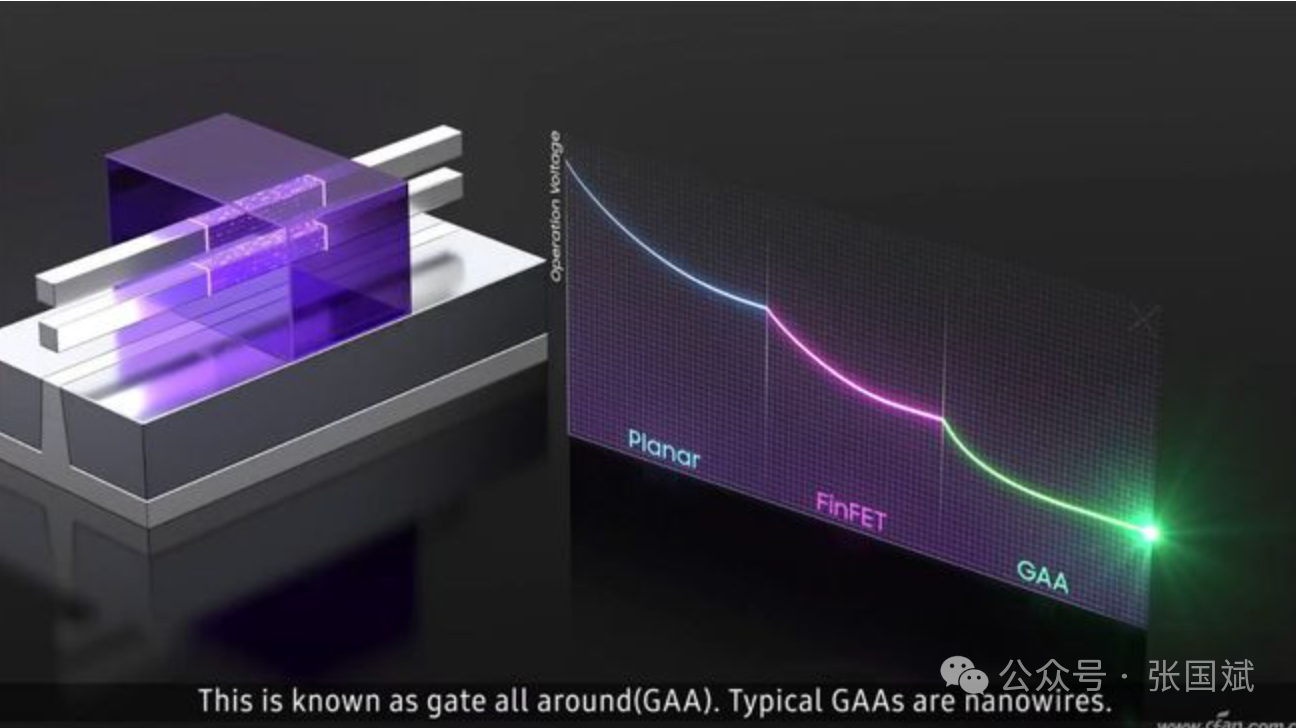

从最早的平面晶体管发展到FinFET(Fin Field-Effect Transistor)的鳍式场效应晶体管再到如今的“GAA FET”(Gate-All-Around Field-Effect Transistor,全环绕栅极晶体管或者叫“全栅场效应晶体管”)。

全环绕栅极晶体管是一种比FinFET更复杂的晶体管结构,它的栅极可从各个侧面接触沟道并实现进一步微缩,就静电学而言它被认为是一种“终极CMOS器件”,其阈值电压可以低至0.3V,3nm GAA FET较之3nm FinFET能以更低的待机功耗实现更好的开关效果。

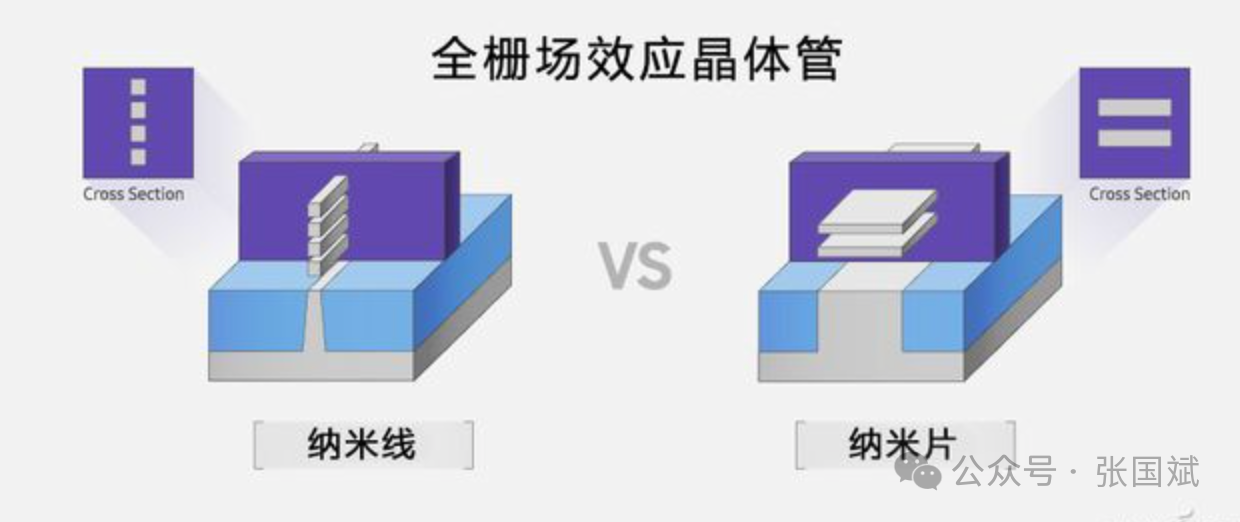

在具体实现上,GAA FET全环绕栅极晶体管根据源极与漏极之间通道的长宽比不同,分为纳米线结构以及纳米片结构两种,后者使用更宽和更厚的线(片)来改进静电特性和驱动电流。三星的3nm GAA就号称采用纳米片结构,而官方对外宣称的技术英文名为Multi-Bridge Channel FET(MBCFET,多桥通道场效晶体管)。

根据曝光的资料,似乎英特尔和台积电走了稍稍不同的技术路线。

台积电的 Gate-All-Around (GAA) FET 中栅极材料完全环绕沟道,这种完全环绕的设计增强了对通过沟道的电流的控制,减少了漏电流,并允许在较低的电压下工作。其特点提高了电流控制能力,降低了漏电流,台积电的GAA技术在提高晶体管性能的同时,也注重了制造工艺的可扩展性和成本效益。

而英特尔的 RibbonFET 采用类似的全栅极设计但有一个独特的转折,RibbonFET 没有采用传统的垂直鳍片,而是采用了纳米片技术,将多个平面纳米片堆叠起来形成沟道。这种设计能更好地控制电流,从而显著提高性能和效率,英特尔的RibbonFET技术则强调了晶体管开关速度的提升、性能密度的提高以及芯片设计的灵活性。RibbonFET 是英特尔先进节点的旗舰创新技术之一,强调了公司在半导体领域重新夺回技术领先地位的承诺。

RibbonFET还将进一步提升芯片设计的灵活性,其沟道可以根据需求加宽或缩窄,从而更适配不同的应用场景,不管是手机还是电脑,游戏还是医疗,汽车还是人工智能,可轻松胜任按需配置。

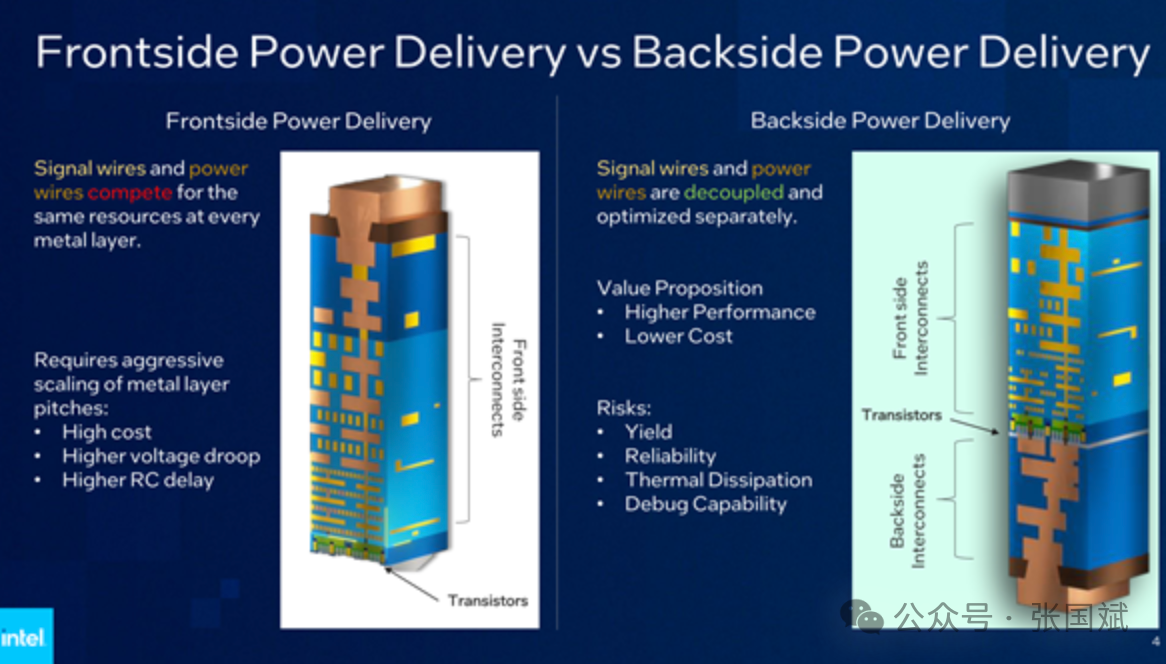

英特尔还有一个技术就是PowerVia背面供电技术,2023年6月,英特尔宣布在业内率先在产品级测试芯片上实现背面供电(backside power delivery)技术。

通过PowerVia背面供电技术,英特尔告别了披萨式的制造方式,让芯片制造第一次涉及两个面:像以前一样,首先制造晶体管,然后添加互连层,接下来则是翻转晶圆并进行打磨,露出连接电源线的底层。英特尔证实,PowerVia背面供电技术的好处是多方面的:

首先,向晶体管供电的路径变得非常直接,可以改善供电,减少信号串扰,降低功耗,将平台电压降低优化30%;

其次,电源线和互连线可以分离开来并做得更粗,同时改善供电和信号传输,解决了晶体管尺寸不断缩小带来的互连瓶颈,实现了6%的频率增益和超过90%的标准单元利用率,对于普通计算机用户来说,这意味着降低能效和提高速度。

测试显示,PowerVia技术确实能显著提高芯片的使用效率,大部分芯片区域的标准单元利用率都超过了90%,同时晶体管体积大大缩小,单元密度大大增加,因此能显著降低成本。此外,PowerVia将平台电压降低了30%,并带来了6%的频率增益。

另外,昨日关于博通测试英特尔Intel 18A工艺的最确切信息是:博通8月收到英特尔代工的晶圆后,在其工程师和高层主管经研究测试结果后,博通的发言人表示,他们“正在评估英特尔晶圆代工(Intel Foundry)提供的产品和服务,尚未做出相关结论”。

而英特尔的发言人则透过声明表示:“英特尔18A正蓄势待发、表现健全且良率佳,我们依旧完全按部就班准备明年开始大量生产。业界多方对英特尔18A大感兴趣,但基于政策,我们对于与客户间的特定对话不做评论。”

一家独大对产业对客户都不是好事,良性的竞争是好事,促进技术的发展。

注:本文为原创文章,未经作者授权严禁转载或部分摘录切割使用,否则我们将保留侵权追诉的权利