随着节点不断缩小,芯片变得越来越复杂,需要更多的工程师团队。为了确保芯片的设计时间不会随之增加,复杂片上系统设计领导者 Sondrel 大力投入研发,以建立创新的建模工具和流程,简化ASIC 设计流程。Sondrel 已将其编入片上系统架构设计所需的十个步骤中。

“(芯片)越复杂,客户就越需要将其片上系统设计外包给像我们这样拥有多学科工程师团队的专业公司,”Sondrel 的首席执行官 Graham Curren 解释道,“Sondrel 已经在许多应用领域搭建了数百个 ASIC,我们拥有足够的经验,确保我们可以使用最新、最好的设计技术。其中许多技术还是我们自己定义的。”

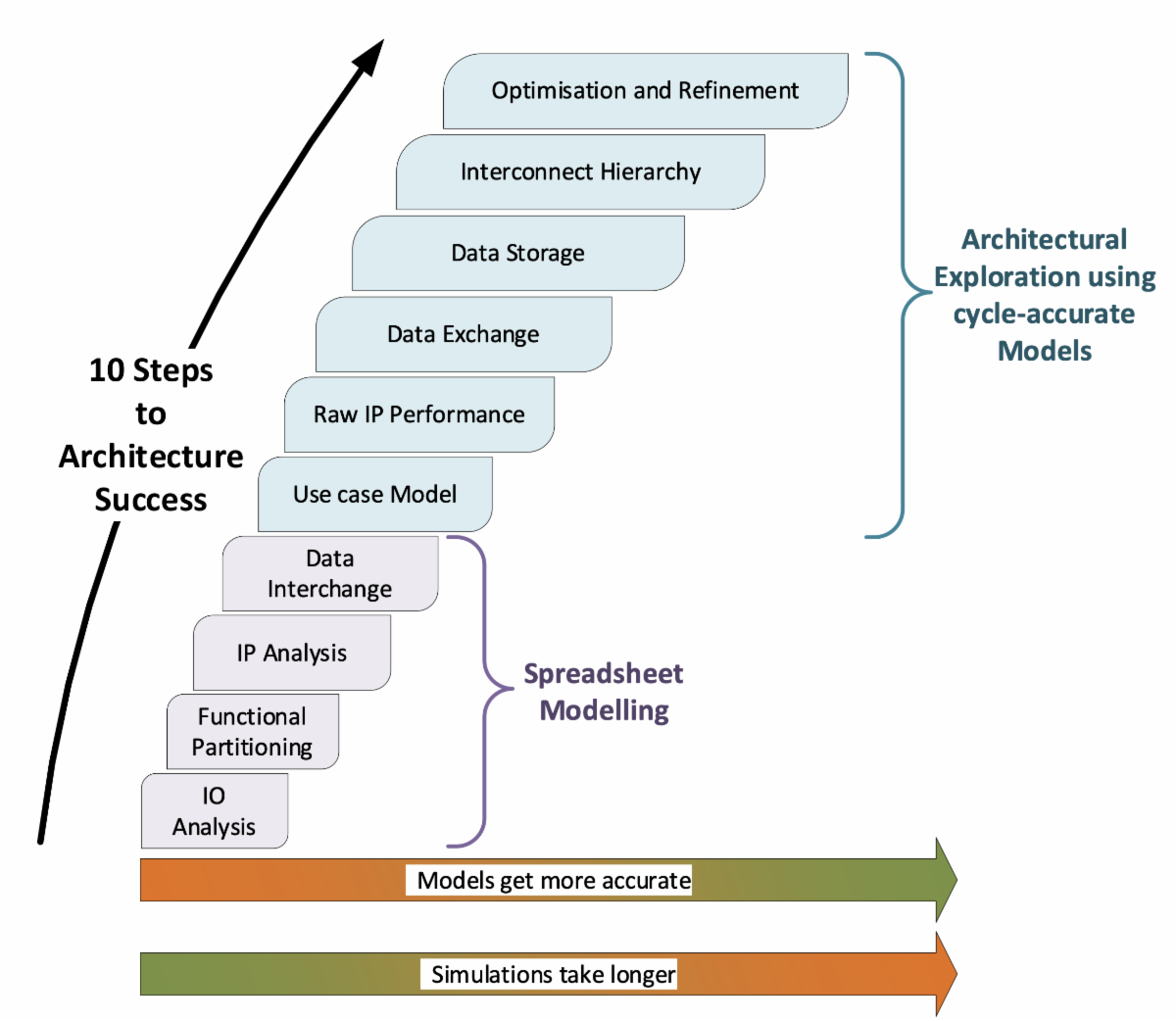

总之,成功设计片上系统架构的策略是:

- 使用分而治之的方法,将问题分解为多个阶段

- 各阶段详细程度的提高,要考虑的探索选项就越少

- 利用建模,解决具体问题

- 按照流程进展所需,集中资源

- 避免浪费仿真时间

- 减少要分析的数据集量

- 减少模拟量和次数,以抵消减速

- 按逻辑顺序考虑问题,以简化因果分析,并减少所需的迭代

- 进行迭代,以发现问题并修复,然后再继续推进,以减少不必要的设计工作。

- 平衡好准确与速度之间的关系。

这 10 个步骤:

1. 确定了数据是什么以及 I/O 约束是什么,例如突发性、延迟、时序和数据格式,用于决定电子表格中捕获的缓冲区要求。

2. 将处理流程分解成多个子任务,并将片上系统的各个部分组合成通用功能。

3. 确定了执行算法步骤需要哪些第三方 IP 块,以及他们需要从数据表中获取多少内存和计算能力。这些数据表可以输入到建模环境中,以便更准确地表示所有 IP 块的功能。

4. 涵盖算法各个部分之间的数据交换方法,例如片上 SRAM 或外部 DDR 存储器,以及片上存储器的小空间 FIFO。SRAM 和 DDR 之间的决定取决于数据的大小以及需要访问的频率,其中大块数据进入外部存储器,小块数据进入 SRAM 或 FIFO。

5. 利用算法的概念图以及算法不同软件阶段的实际模拟对象,对各种不同阶段的软件表示。这些需要做好延迟和处理周期等设置,并由名为通道的对象连接,通道可以指示具体的顺序。

6. 在构建好完整算法的所有模拟对象后,可以运行仿真,查看是否已捕获算法的正确顺序。

7. 使用带有 VPU(虚拟处理器单元)的硬件平台模型,将运行步骤 5 的软件,各自拥有自己的本地内存。这里可以考虑接口时序,使用分配的通道定义通信域并进行评估。还可以验证 VPU 的配置是否正确。

8. 为各 VPU 准备可用的内存,并将其重新建模,利用公共内存控制器连接到外部存储器。这样可以更准确地表示最终系统中所有 VPU 和内存的连接性。

9. 添加互连结构。VPU 和内存控制器之间的直接连接被互连结构取代。同时还评估了这对时序和性能的影响。然后调整互连结构,以满足所需的性能,并重复先前的阶段,以达到所需的结果。

10. 建立一种良好的工作模型,通过简单地调整设置,就可以运行模拟,识别各种瓶颈、系统中存在的约束,以及各种需调整的参数,以提高吞吐量并减少片上系统延迟。运行只需要几分钟到一个小时即可完成,因此变体测试非常简单、便捷。

前四个步骤可以通过计算在纸上或电子表格上完成,以理解片上系统的输入/输出数据流以及它们的特性。最后六个步骤则是基于仿真,构建软件模型并运行仿真,以生成有关系统的结果。

有关这方面更多的信息,请访问: www.sondrel.com/solutions/white-papers

关于Sondrel

Sondrel成立于2002年,是集成电路各阶段设计方面值得信赖的合作伙伴。其在定义和设计专用集成电路方面的咨询能力屡获殊荣,为其将设计转化为经过测试的批量封装硅芯片的一站式服务提供了有力补充。整个供应链流程的单点联系,确保风险低,上市时间快。Sondrel总部位于英国,其通过在中国、印度、法国、摩洛哥和北美的办事处,为全球客户提供支持。更多信息,请访问www.sondrel.com