随着算力需求的多元化以及安全攻击技术的不断演变发展,在硬件层面强化安全控制与管理成为数据中心高效运营的重要支撑。但同时,多元算力带来硬件平台设计的组合复杂多样,相应的安全管理单元往往需要经过更长时间的设计与测试验证,不利于研发资源的集约利用与产品的快速迭代。为了解决上述问题,浪潮信息加入了 OCP Hardware Management Module (硬件管理模块)项目组,参与DC-SCM2.0规范的制定与完善,在产品研发中对DC-SCM标准进行了设计实现,并在x86和ARM平台实现了DC-SCM标准的验证和实践。

模块化成趋势 DC-SCM 规范推动安全管理单元标准化

作为数字经济时代新的生产力,算力为激活数据要素潜能以及推动各行各业数字化转型注入新动能。但与此同时,数据中心平台的多元化趋势越发明显,Intel、AMD、ARM、Power等平台将在很长一段时间内在数据中心共存,而每一代CPU都有单路、双路、四路、八路,以及1U、2U、4U等各种形态的产品,每一款产品中又都要进行内存、存储、加速器、安全管理器件的设计,平台设计组合迅猛增长。

如果按照传统的研发模式,每一代平台组合都需要长时间的设计和测试验证,而且CPU和安全管理芯片的更新迭代又相互制约,进而影响了平台性能的充分发挥。虽然不同平台存在较大的差异化,但平台的安全管理特性基本相似,因此,以标准化模块设计方式,兼容不同平台的安全管理需求,降低研发资源的重复投入,加快产品迭代速度,成为数据中心应需而变,不断升级的重要发展趋势。

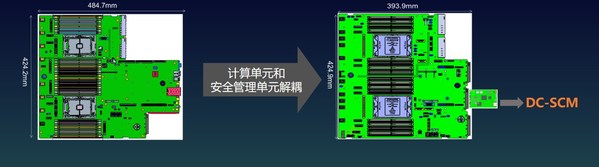

DC-SCM(DataCenter-ready Secure Control Module)项目正是由此而来,作为OCP Hardware Management Module项目组提出的首个数据中心安全管理单元模块化的通用规范,此规范实现了计算单元无状态化,即计算单元和安全管理单元解耦(如下图),将常见的管理、安全和控制功能从主板分离,转移到较小的通用外形模块中,通过连接器实现与主板相连,而该模块包含之前在主板上容纳的所有固件状态( BMC、TPM、Boot Flash、ROT等)。

DC-SCM通过安全管理单元的模块化,大大降低主板的设计难度,节省设计和验证时间,支持在设计中采用成本较低的板材,从而降低整机成本。同时,DC-SCM实现了BMC和ROT发展周期与CPU迭代的解耦,加快安全管理芯片和CPU的更新迭代,并实现跨平台兼容。DC-SCM标准加入了对新技术和管理接口的支持,如多节点服务器设计,添加PCIe、USB3.0和I3C接口等,极大提升数据中心平台的可扩展性和使用寿命。

实践出真知 浪潮信息参与DC-SCM2.0规范的制定与完善

作为开放计算的倡导者与推动者,浪潮信息于2021年12月加入了 OCP Hardware Management Module 项目组,与Intel、Ampere、Google、Microsoft等公司一起,参与DC-SCM2.0这一全球硬件管理规范的完善。在加入DC-SCM2.0工作组后,浪潮信息贡献了大量工程师资源、设计实践和用户反馈等,积极参与对规范的测试实践,推动DC-SCM2.0规范的不断完善和普及。

在OCP Hardware Management Module 项目组成员的集体协作下,DC-SCM2.0对比上一代标准增加了多种新特性,例如支持更多接口标准,使用范围更加广泛,适应更多新技术;增加可选的双节点支持功能,实现CPU分区管理;采用LTPI协议串行传输更多信号,进一步缩减PIN;提高信号传输速度,降低延迟;提高电气兼容性、改善结构等。

浪潮信息在自身的产品研发过程中,对DC-SCM标准进行了大量的设计实现,并分别在x86平台、ARM平台上对2.0标准和1.0标准进行了验证,利用DC-SCM标准增强了服务器安全管理能力,加快了对新技术的支持与更新迭代。此外,浪潮信息还积极应用DC-SCM2.0规范中的新技术方向,进一步强化数据中心安全管理体系的建设。

目前,浪潮信息已在多个新兴技术领域推动与开放计算项目的融合,促进整机柜、OAI/OAM、边缘、存储、网络、液冷等前沿应用和技术标准化与产业化。参与OCP Hardware Management Module 项目组DC-SCM2.0规范的制定与完善,并牵头服务器全部国标、OAM规范、天蝎标准、边缘OTII规范等,同时推动技术标准产品化,率先向社区贡献了多款产品,以供全球厂商借鉴。未来,浪潮信息将继续坚持开放、开源的技术路线,持续推动开放计算产业化,加速开源技术普惠。

稿源:美通社