在 IEDM 2021 上宣布:确认在 16 nm FinFET 逻辑工艺嵌入式 STT-MRAM 测试芯片上降低功耗并提高写入操作速度

12月14日——瑞萨电子公司 (TSE:6723) 是先进半导体解决方案的主要供应商,今天宣布开发两种技术,可减少自旋转移矩磁性随机存取存储器 (STT-MRAM) 写入操作的能量和电压施加时间,以下简称 MRAM)。在 16 纳米 FinFET 逻辑工艺中嵌入 MRAM 存储单元阵列的 20 兆位 (Mbit) 测试芯片上,写入能量减少了 72%,电压施加时间减少了 50%。新技术有: 1)采用斜坡脉冲应用的自终止写入方案,根据每个存储单元的写入特性自动自适应终止写入脉冲;2) 用于优化位数的写入序列,同时向其施加写入电压。结合,

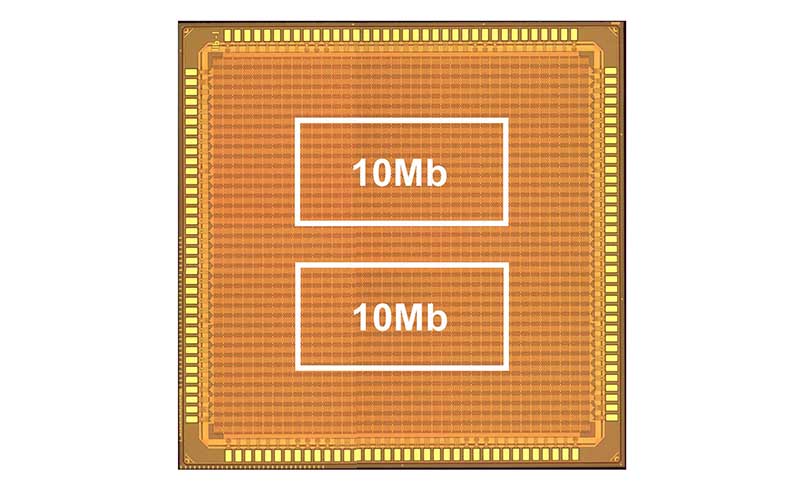

嵌入式STT-MRAM芯片照片

瑞萨电子于 12 月 13 日在 12 月 11 日至 15 日在旧金山举行的 2021 年 IEEE 国际电子器件会议 (IEDM) 上展示了这些成就。

近年来,随着物联网技术的加速普及,对降低端点设备中使用的微控制器单元 (MCU) 的功耗有着强烈的需求。与闪存相比,MRAM 用于写入操作所需的能量更少,因此特别适合数据更新频繁的应用程序。然而,随着 MCU 对数据处理能力的需求激增,改善性能和功耗之间的权衡的需求也在增加。因此,进一步降低功耗仍然是一个紧迫的问题。

下文描述了满足这一需求的新 MRAM 写入技术。

1. 使用斜率脉冲的自终止写入方案

二进制数据通过使用磁隧道结 (MTJ) 器件的高阻态 (HRS) 和低阻态 (LRS) 分别表示值 1 和 0 来存储在 MRAM 中。之前,已经提出了一种自终止写入方案来减少写入能量和电压施加时间,通过在固定写入电压施加期间通过监视存储单元电流来检测写入完成,并且自动停止写入电压的施加。然而,与诸如存储单元特性的变化和比较器电路检测写入完成的检测精度等因素相关的问题阻碍了稳定且一致的写入完成检测的成功实现。

为了解决这些问题,在传统的自终止写入中,MTJ 从 HRS 变为 LRS 的写入操作期间不施加固定电压,而是采用了随时间逐渐上升的斜率电压。这使得可以稳定且一致地检测写入完成。即使由于存储单元特性的变化和其他因素,存储单元电流在状态转变之后没有立即达到检测器电路的检测电平,随后写入电压的逐渐上升也会增加存储单元电流。这最终会超过检测电平,从而能够检测到写入完成并停止施加写入电压。

在状态转变为相反方向的写入操作期间,从LRS到HRS,存储单元电流从大电流变为小电流,因此使用斜率电压脉冲的写入完成检测是不可能的。因此,采用电流源电路以倾斜的方式增加写入电流,通过电压检测电路监测写入电压,判断是否超过预设判断电压来检测写入完成。

2. 同时写位数优化技术

以前,MRAM 写入电压是根据存储单元特性变化中最差的位写入特性来确定的。这意味着需要高写入电压,并使用电荷泵电路来产生它。为了减少电荷泵电路的面积和功耗,例如将MRAM宏的写入单元分成四组或更多组,依次施加每个写入脉冲。然而,这增加了分区数的写入电压施加时间。

为了解决这个问题,瑞萨专注于通过允许高达 10% 的写入失败位来大幅降低写入电压这一事实。首先,通过降压转换器电路使用从MCU的IO电压产生的低写入电压,同时向写入单元中的所有位施加写入电压。在这一步中,使用上一节中描述的带有斜坡脉冲的自终止写入方案,根据各个位的写入特性执行自终止写入操作。接着,利用电荷泵电路产生的高写入电压对剩余的10%的位执行写入操作。由于采用这种技术,写入电压的施加分两个阶段完成,与将写入单元分成四组或更多组的传统方法相比,整体写入电压施加时间可减少50%或更多。此外,对于绝大多数位而言,该技术在写操作时不需要耗电的电荷泵,而是使用降压转换器从外部电源电压获得的写电压。这有效地减少了写入能量的消耗。

在采用 16 nm FinFET 逻辑工艺的 20 Mbit 嵌入式 MRAM 存储单元阵列测试芯片上进行的测量中,证实上述两种技术的组合可将写入能量降低 72%,并将写入脉冲应用时间缩短 50%。

瑞萨不断开发增量技术,旨在将嵌入式 MRAM 技术应用到 MCU 产品中。展望未来,瑞萨将努力进一步提高容量、速度和电源效率,以适应一系列新应用。

关于瑞萨电子公司

瑞萨电子公司(东京证券交易所股票代码:6723)通过完整的半导体解决方案提供值得信赖的嵌入式设计创新,使数十亿连接的智能设备能够改善人们的工作和生活方式。作为微控制器、模拟、电源和 SoC 产品的全球领导者,瑞萨电子为广泛的汽车、工业、基础设施和物联网应用提供全面的解决方案,帮助塑造无限的未来。在renesas.com 上了解更多信息。在LinkedIn、Facebook、Twitter、YouTube和Instagram 上关注我们。